# TECHNOLOGY LEADERSHIP BIPOLAR MICROPROCESSOR

Expand your present 8080A based system, yet use all of the software you've developed, with the Signetics 8080A Emulator. Built with the 3001/3002 bipolar bit slice microprocessor, the emulator executes all 8080 instructions at speeds from 2 to 9 times faster than the 8080, uses a single 5 volt supply, a single phase clock, and is microprogram expandable.

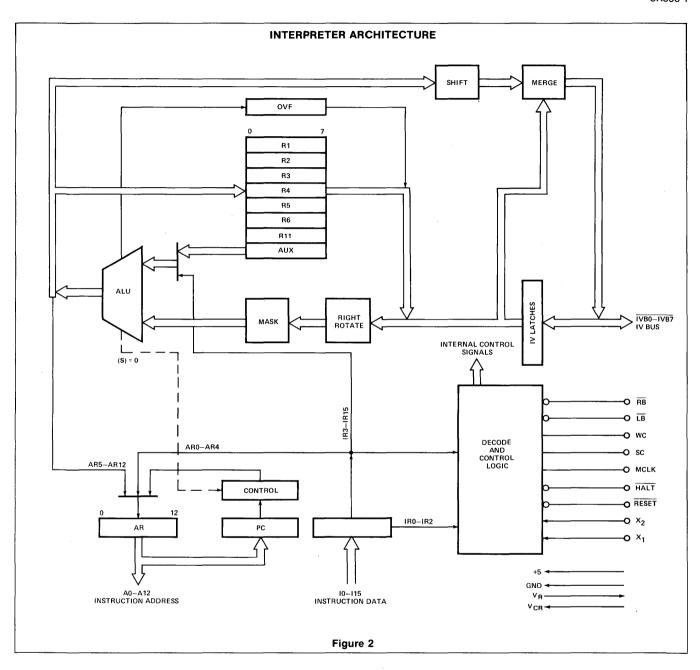

The emulator kit comes complete with all parts needed to construct this bipolar replacement for the 8080A, 8228, 8224 and 8212, including preprogrammed PROMS and P.C. board. The accompanying manual tells how to build it, how to use it, and gives a thorough tutorial description of the design and theory of operation. With this \$299 kit you can have 8080A emulation in 6 hours. Order 3000KT8080SK.

Reach for this book anytime you need information on bipolar microprocessors. The following pages have everything here for quick easy reference to data sheets on:

- Bit Slice Microprocessor

- Sequencers

- Microcontroller

- Selected Interface Products

with selection guides and summary data sheets for:

- Memory Products (including FPLA)

- Analog Interface Products

- Interface Circuits

- System Logic

and references and data sheets on:

- Development Systems

- Development Software

and data sheets on kits and application notes.

Yes, it's all here.

Signetics is the total memory supplier. To meet the needs of microprocessor users and system designers, Signetics offers a complete line of memory products.

Here are a few examples:

- Bipolar and Static MOS RAMS

Bipolar 8 to 1024 bits, access times to 35ns

MOS Static 256x4 to 4096x1\*, access time to 85ns

- Dynamic MOS RAMS To 16Kx1

- Bipolar and MOS ROMS and PROMS

Bipolar and MOS Static ROMS to 16K bits

Bipolar PROMS to 16K bits\*

MOS EROMS\* to 8 K bits

Character Generators

- Bipolar FPLA/PLA

- Bipolar CAMS and Register Files

Selection guides are provided in the Bipolar Microprocessor book. For more information send for the full list of total MOS and bipolar memory line.

\*Available 1st quarter 1977

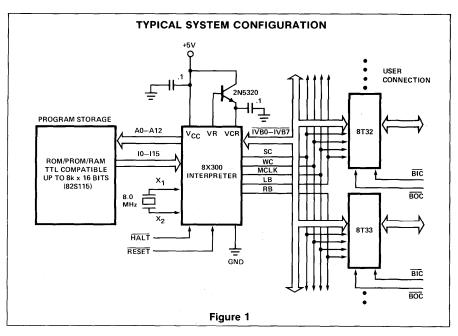

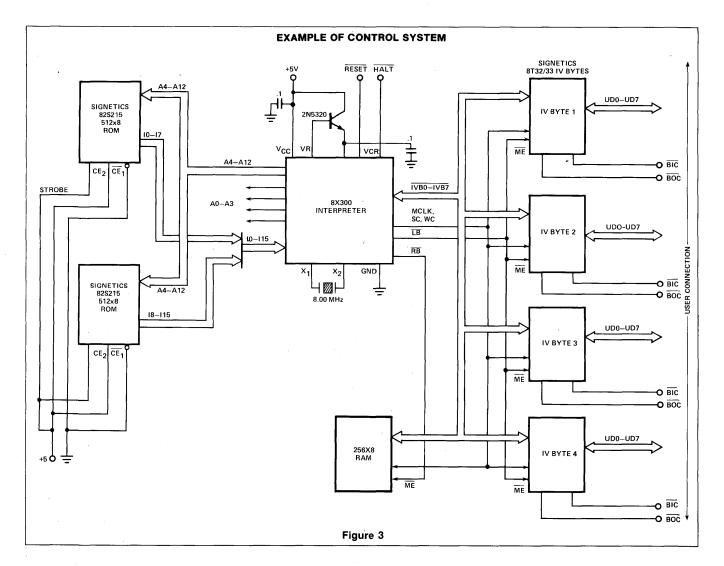

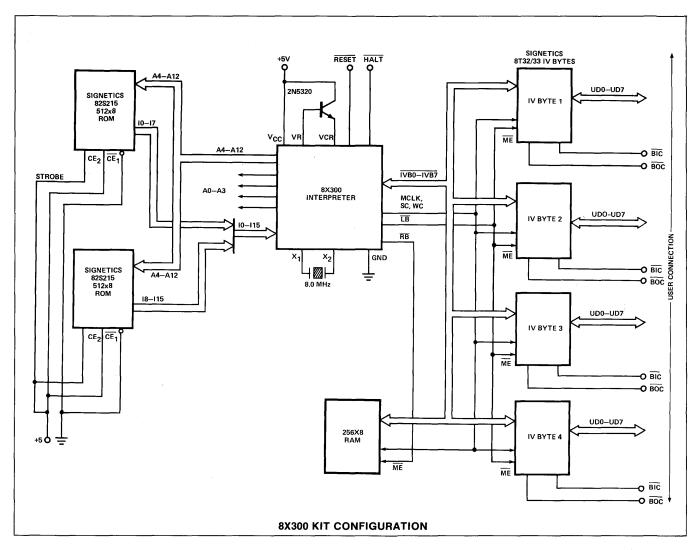

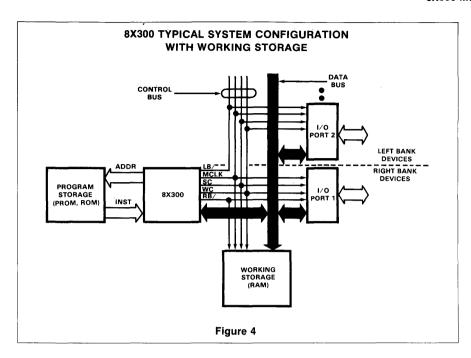

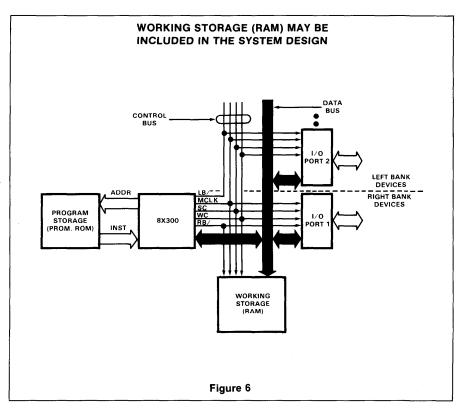

Complete with the 8X300, clock crystal, 4 I/O ports, 256 bytes of working storage, 512 words of program storage, and P.C. board with wire wrap area, the kit is ready to be used as a basic starter system for your own controller design. There are 450 empty PROM locations that can be used to hold the program for your controller using this, the industry's first high speed (Schottky) complete 8-bit microprocessor. The remaining 62 locations contain diagnostics which can be used to check out the board or monitor the 8X300 through Single Step and Instruction Jam features of this kit. This \$299 kit is a fast, inexpensive way to get started with the 8X300. **Order 8X300KT100SK**.

Making your microprocessor system do its job requires interface to the outside world. Signetics Analog Interface products link your microprocessor to displays and sensors. Here are a few examples:

- Peripheral Interface

Drivers to 80 volts (DS3611 series—UDN5711 series)

Line Receivers and Drivers

- Display Interface

Display Decoder/Drivers to 100 volts—DM8880/-1

NE584, NE585, NE582

- D/A Converters to 8 bits MC1408-8, NE5008/9

- Comparators

NE521/522, LM111/211/311, LM119/219/319, LM139/239/339, LM193/293/393

- Timers NE553/554/555/556

plus an assortment of popular voltage regulators, phase locked loops, amplifiers and other specialized circuits.

Selector guides are provided in the Bipolar Microprocessor book. For more information send for Signetics Analog manual for data sheets and application notes.

An easy way to get a complete set of parts for a bit slice microprocessor is with this kit of parts. An 8-bit processor can be constructed using the four 3002's with microcontrol provided by the 3001 and two 82S114's contained in the kit. In addition you get two 8T26A bus transceivers and an 8T31 bidirectional I/O ports to round out the parts complement. For your start in bit slice microprocessors, get this \$230 value with data book for \$100. **Order 3000KT100SK**.

Development of complicated microprocessor based systems and controllers can be difficult, but with the help of appropriate support systems the work can be considerably eased. Signetics presents its own as well as commercially available support products for the new Bipolar Microprocessor book. Send for one on your company letterhead today. We'll tell you about the 8X300 Microcontroller Simulator, PROM Programmers, FPLA Programmers, the Cross Assembler and other aids for system development that will be invaluable to you in both time and money.

Signetics "Answermen" are there to solve your problems not just sell you a microprocessor. Microprocessor Application Specialists, 9 in all, located in strategic parts of the country serve customers in all corners of the continental United States. Well versed in Signetics MOS, bipolar bit slice and bipolar microcontroller microprocessors through regular intensive factory training, these "Answermen" have no limit in technology they may draw upon to provide you with a cost effective approach to your task. They may suggest the 2650, the 3002, the 2901-1 or the 8X300 in combination with System Logic, Interface and support circuits in an architecture that can do the job with the least cost. And for more difficult problems, the "Answermen" may draw on the factory staff of application experts. Call an "Answerman" for a discussion of your specific needs or for a seminar on the Signetics product line. "Answermen" are located in:

Sunnyvale

Boston

Los Angeles

Irvine

New York

Pompano Beach

Minneapolis

Philadelphia

Dallas

## TABLE OF CONTENTS

| Chapter 1 BIPOLAR BIT SLICE FAMILY                                                    |      |

|---------------------------------------------------------------------------------------|------|

| Introduction                                                                          |      |

| 8X02 Control Store Sequencer Data Specifications                                      |      |

| 3000 Series Data Specifications                                                       |      |

| SN3001 Microprogram Control Unit                                                      |      |

| SN3002 Central Processing Element                                                     | 31   |

| Kits                                                                                  |      |

| 3000KT1000 Designer's Evaluation Kit                                                  |      |

| 3000KT8080SK 8080 Emulator Kit                                                        |      |

| Microassembler                                                                        | 44   |

| Chapter 2 BIPOLAR FIXED INSTRUCTION MICROPROCESSOR                                    | 45   |

| Introduction                                                                          | 47   |

| 8X300 Interpreter Data Specifications                                                 | 48   |

| 8X300AS100SS MCCAP 8X300 Cross Assembler                                              | 59   |

| Peripheral Circuits                                                                   |      |

| 8T32/33/35/36 8-Bit Latched Addressable Bidirectional I/O Port Data Specifications    | 60   |

| 8T39 Bus Expander Data Specifications                                                 | 67   |

| Kits                                                                                  |      |

| 8X300KT100SK Designer's Evaluation Kit for Fixed Instruction Bipolar Microprocessor   | 71   |

| Support Software                                                                      | 73   |

| Chapter 3 STANDARD SUPPORT CIRCUITS                                                   | 75   |

| Introduction                                                                          | 75   |

| Memories                                                                              |      |

| Memory Product Summary                                                                | 77   |

| Interface Logic                                                                       |      |

| Interface Product Summary                                                             | 79   |

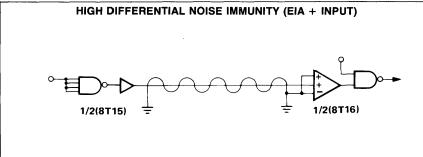

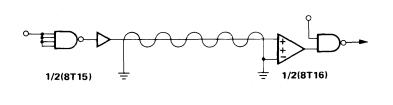

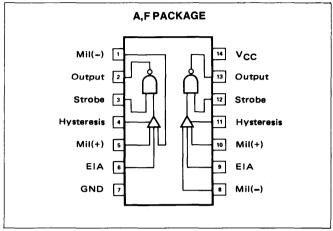

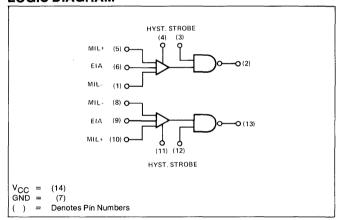

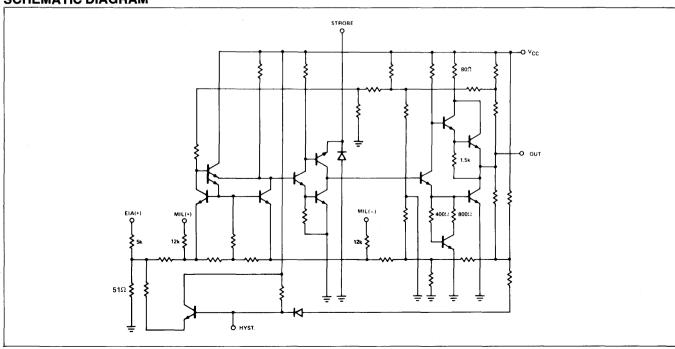

| 8T15 Dual EIA/Mil Line Driver                                                         | 83   |

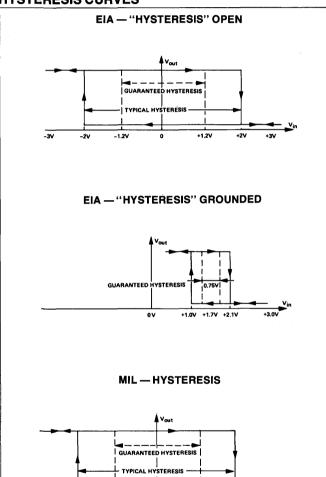

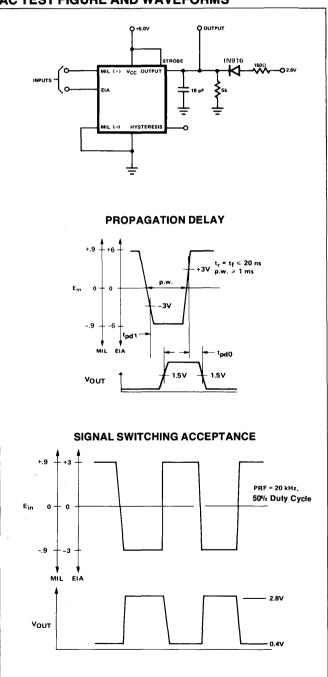

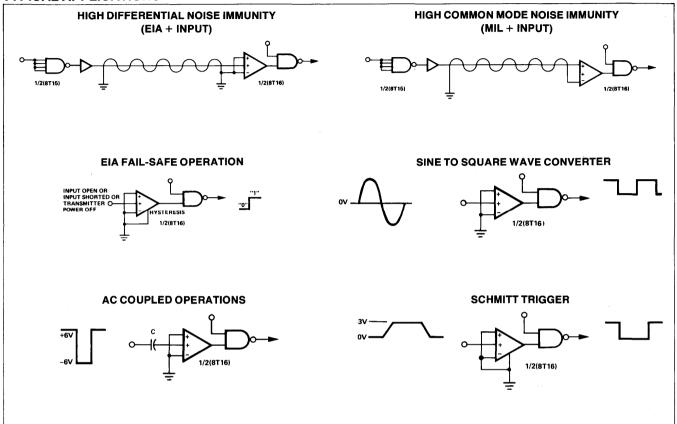

| 8T16 Dual EIA/Mil Line Driver with Hysteresis                                         | 85   |

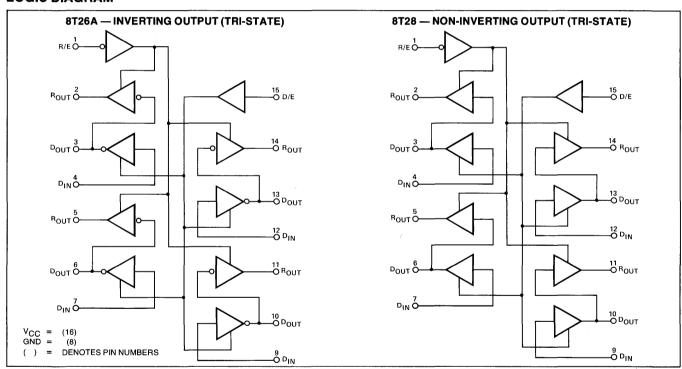

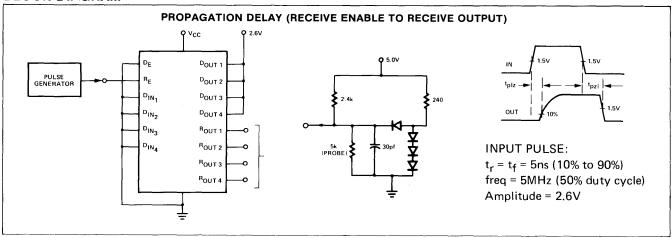

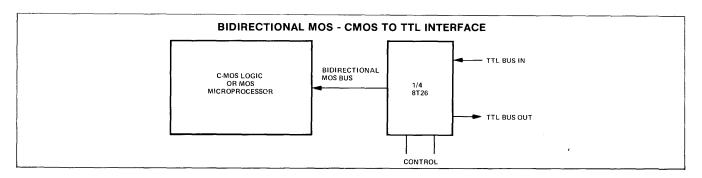

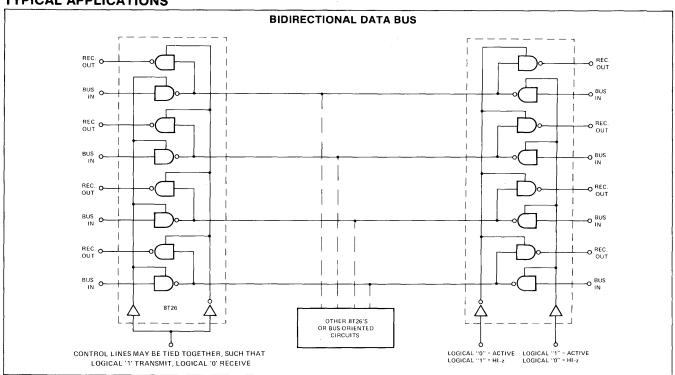

| 8T26A/28 Tri-State Quad Bus Receivers                                                 | 88   |

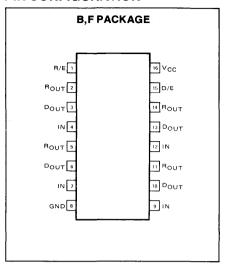

| 8T31 8-Bit Bidirectional I/O Port                                                     | 91   |

| 8T34 Tri-State Quad Bus Transceiver                                                   | 94   |

| 8T95/96 Tri-State Hex Buffers                                                         | 96   |

| 8T97/98 Tri-State Hex Inverters                                                       | 96   |

| Logic                                                                                 | 30   |

| 54/74 Series TTL Product Summary                                                      | 99   |

| 8200 Series TTL Product Summary                                                       |      |

| Logic Function Selector Guides                                                        |      |

| System Logic                                                                          | 100  |

| Introduction                                                                          | 111  |

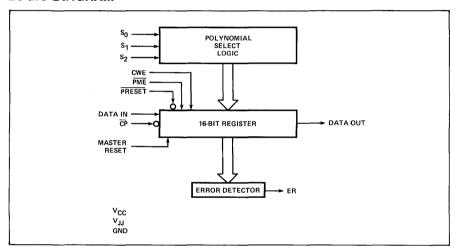

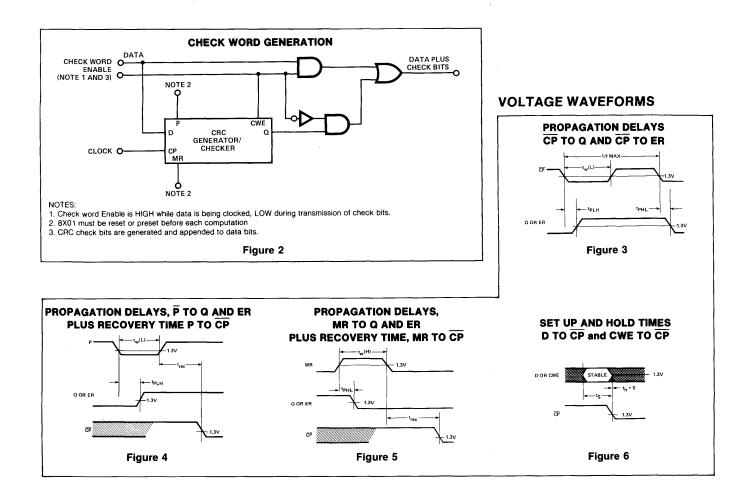

| 8X01 CRC Generator Checker                                                            |      |

|                                                                                       |      |

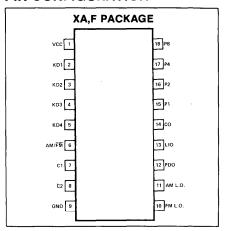

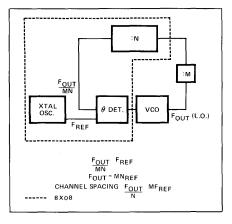

| 8X08 Frequency Synthesizer                                                            | 110  |

| Analog Product Summary                                                                | 121  |

|                                                                                       | 123  |

| 3000 Series Microprocessor                                                            |      |

| AH1 A Guide to the Selection of Support Components for the Series 3000 Microprocessor | 126  |

|                                                                                       | 130  |

| MP1 A User's Guide to the Series 3000 Microprocessor                                  |      |

| MP2 How to Design with the Control Store Sequencer 8X02                               | 142  |

| 8X300 Microcontroller                                                                 | 4 47 |

| AH3 Input/Output Design                                                               | 147  |

| AH4 8X300 Applications                                                                | 149  |

| MP3 Understanding the 8X300 Instruction Set                                           | 164  |

| SP1 The 8X300 Cross Assembly Program                                                  | 171  |

| 8X300 A Fast Microprocessor for Control Applications                                  | 178  |

| Chapter 5 DEVELOPMENT SYSTEMS AND PROGRAMS                                            | 185  |

| Introduction                                                                          | 187  |

| Compatible Products                                                                   | 187  |

| Chapter 6 MILITARY                                                                    | 189  |

| Introduction                                                                          | 191  |

| Microprocessor Support Circuits                                                       | 194  |

| Military Memories                                                                     | 195  |

| Military Logic                                                                        | 196  |

| Military Analog                                                                       | 199  |

9

### CHAPTER I BIPOLAR BIT SUCE FAMILY

#### BIT-SLICE MICROPROCES-SOR SERIES

#### Microcontrol and Arithmetic Units

The introduction of the Signetics Bit-Slice Microprocessors has brought new levels of high performance to microprocessor applications not previously possible with MOS technology. Combining the Schottky bipolar microprocessors with industry standard memory and support circuits, microinstruction cycle times of 100ns are possible.

In the majority of cases, the choice of a bipolar microprocessor slice, as opposed to an MOS device, is based on speed or flexibility of microprogramming. Starting with these characteristics, the design of the Signetics slice microprocessors has been optimized around the following objectives:

- Fast cycle time

- All memory and support chips are industry standard

- Cooler operation

- Lower total system cost

Furthermore, systems built with large-scale integrated circuits are much smaller and require less power than equivalent systems using medium and/or small scale integrated circuits.

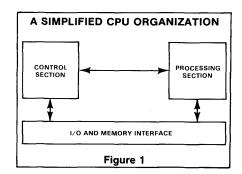

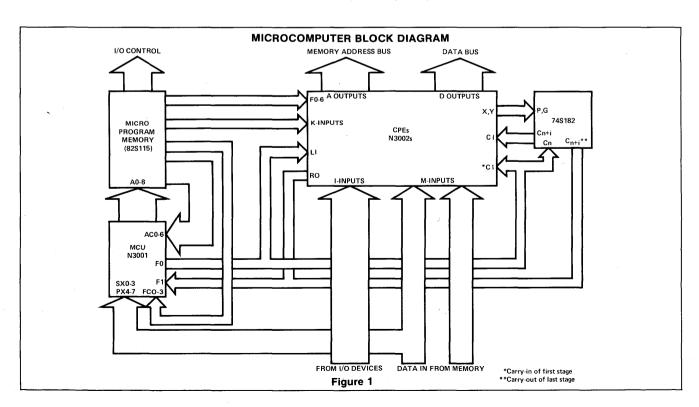

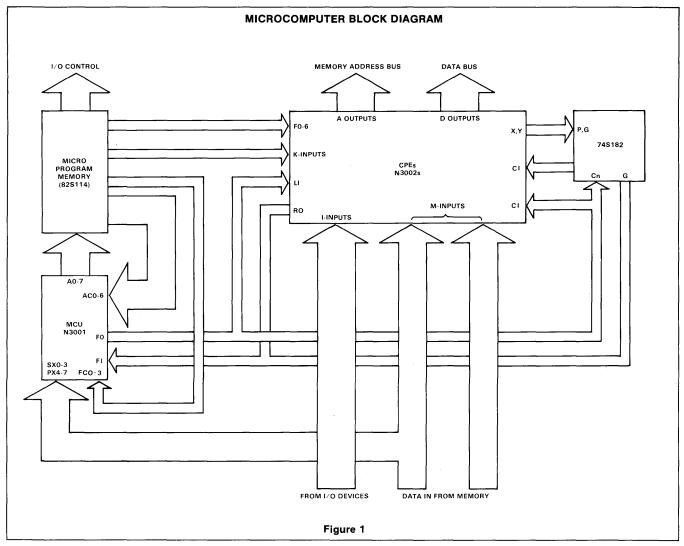

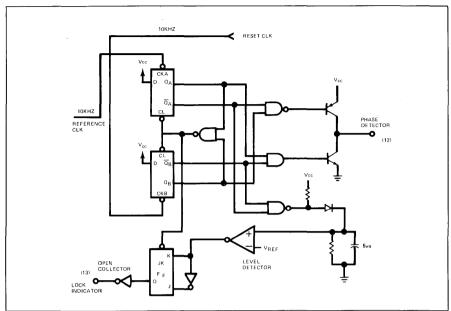

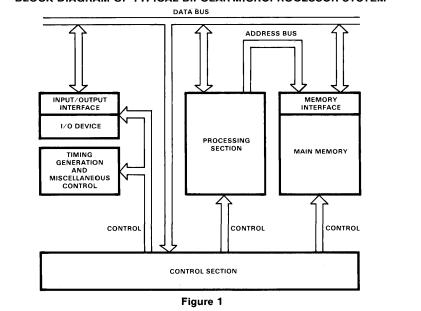

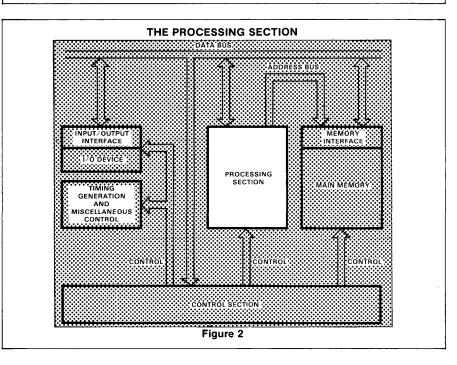

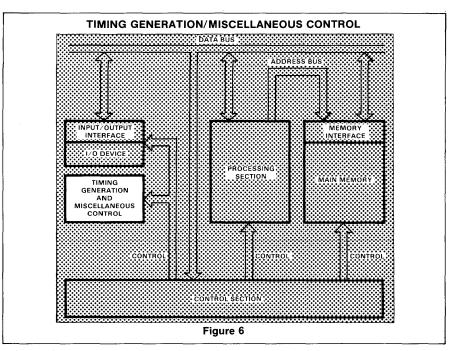

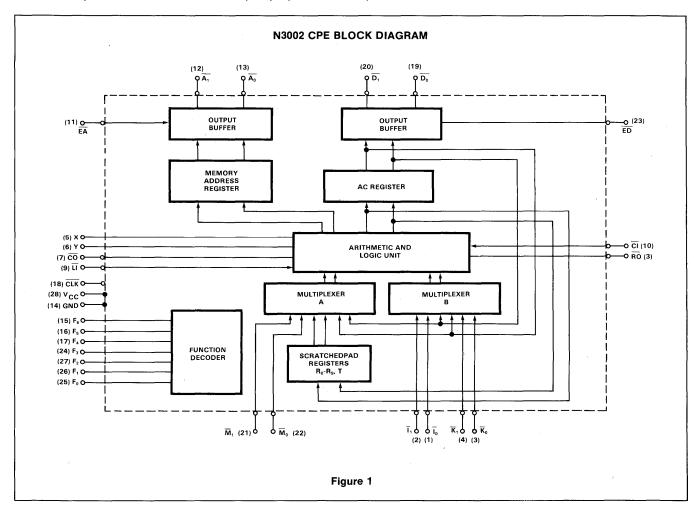

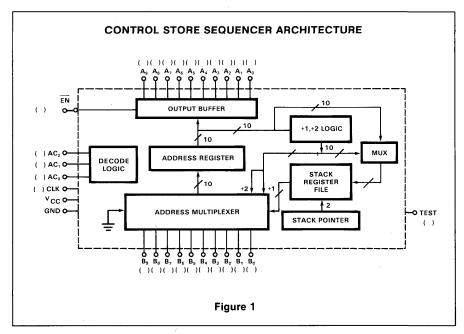

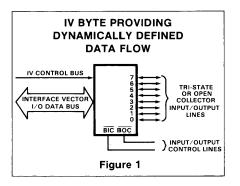

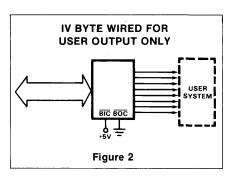

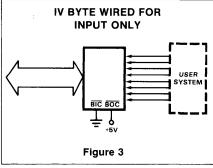

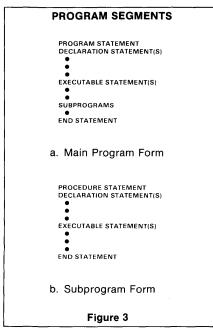

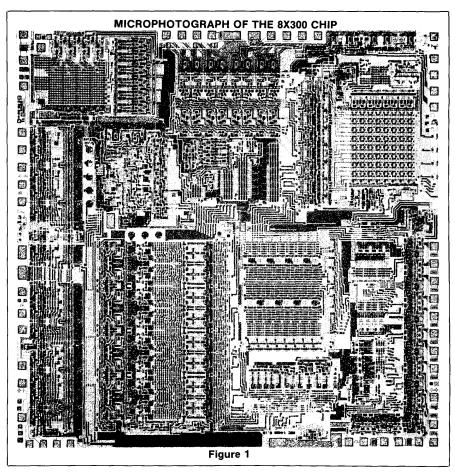

Typically, slice microprocessors are employed in the realization of the Central Processing Unit (CPU) of a computer or for implementing dedicated smart controllers. The generalized and simplified structure of a CPU or "Smart" controller can be typically classified into 3 distinct but interactively related functional sections. These sections are generally referred to as the Processing section, the Control section, and the I/O and Memory Interface section. A simplified block diagram of a CPU is illustrated in Figure 1.

The major functions of the Processing section are to:

- · provide data transfer paths;

- manipulate data through logic and arithmetic operations;

- provide storage facilities such as a register file; and

- generate necessary status flags based on the kind of operation performed by the ALU.

The major functions of the Control section are to:

- initiate memory or I/O operations;

- · decode macroinstructions;

- · control the manipulation and transfer of data;

- · test status conditions; and

- · sample and respond to interrupts.

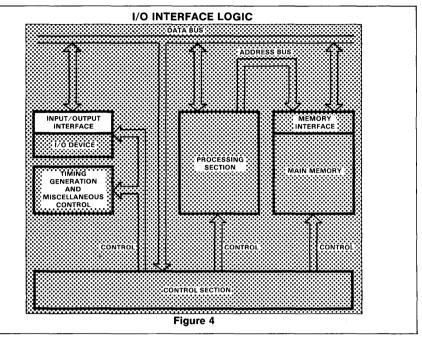

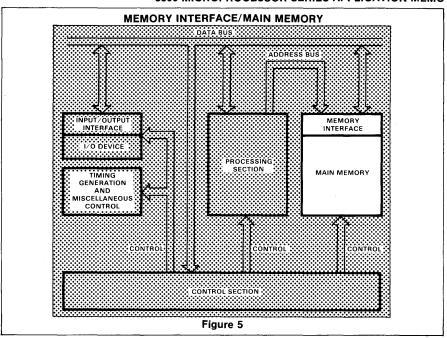

The major functions of the I/O and Memory Interface section are to:

- multiplex data to the proper destination;

- · provide bus driving/receiving capability; and

- provide latching capability.

With state-of-the-art bipolar Schottky technology, high-performance microprocessors are designed to perform functions of the Processing section. Due to the limitation on the number of pins and chip size, the overall Processing section is partitioned into several functionally equivalent slices. In today's bipolar microprocessor market, 2-bit and 4bit slice architecture predominates. Each architecture type has its uniqueness but, in general, a slice contains a group of general purpose registers, an accumulator, specialpurpose register(s) ALU and related status flags. All of these elements constitute the Processing section of a CPU. The flexibility of slice components allows the designer to construct a processing section of any desired width as required by his application.

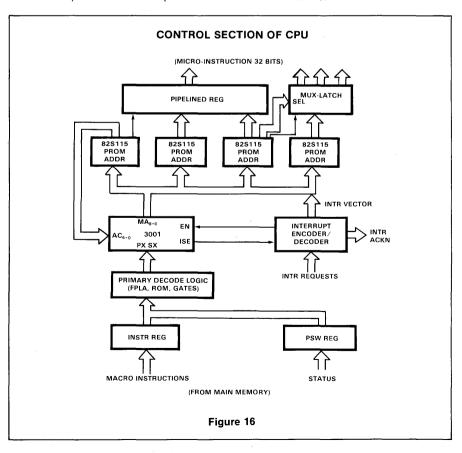

The Control section of the CPU is more complex in design. Typically this section includes the macroinstruction decode logic, test-branch decode, microprogram sequencing logic, and the control store where the microprogram resides. Aside from the microprogram, the remaining portion of the Control section (macroinstruction decode and test-branch decode and sequencing logic), does not lend itself to efficient partitioning into vertical slices. This is due to the random nature of the logic usually found in the Control section. However, horizontal functional grouping is possible. For example, the macroinstruction decode and testbranch decode logic can now be replaced by the FPLA (Field Programmable Logic Array); the random logic traditionally

needed to implement the microprogram sequencing can now be replaced by the Microprogram Control Unit; and, of course, the microprogram can be stored in high density PROMs or ROMs. Since the designer must define his own microstructure, the slice microprocessors permit fundamental optimizations to be made. With slice hardware, the designer may have no macroinstructions at all, placing all of the program in PROM for dedicated control applications. Or he may define, as required, any number of macroinstructions selected specifically for his particular processor purpose. Various minicomputers and several MOS microprocessors have been emulated using slice hardware.

The I/O and Memory Interface section consists mainly of I/O ports, high power bus drivers, receivers, and some temporary register storage facilities. Bidirectional and tri-state devices are the most popular logic elements for implementing this interface structure

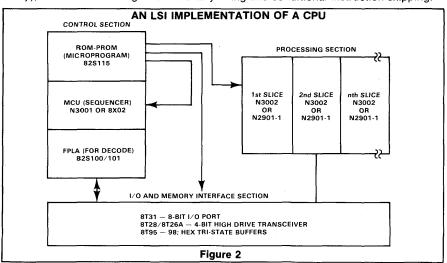

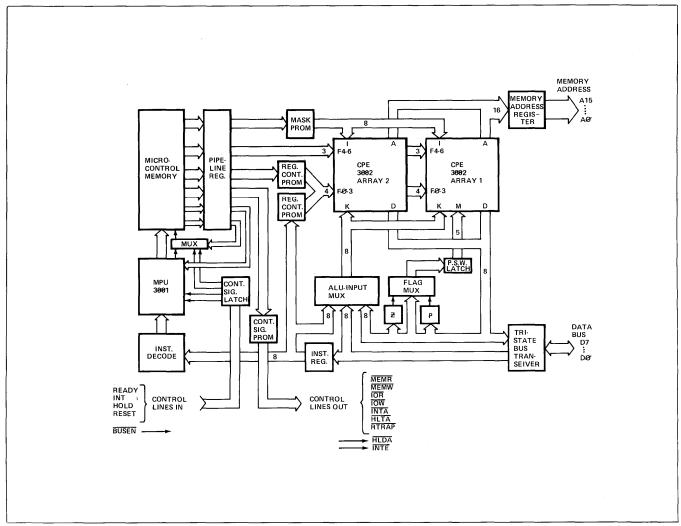

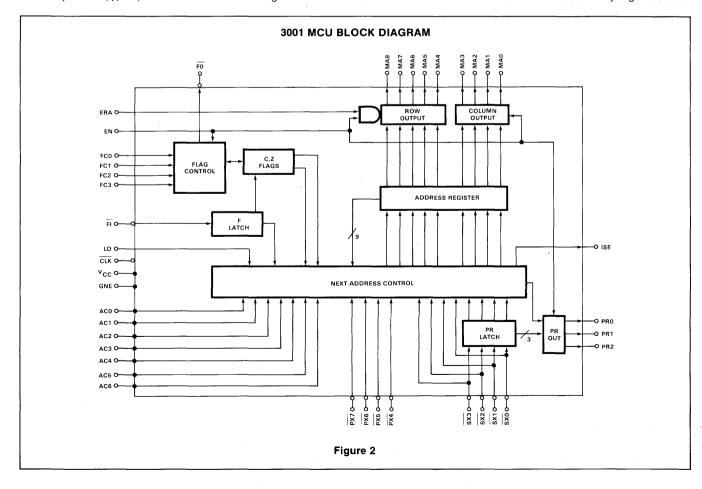

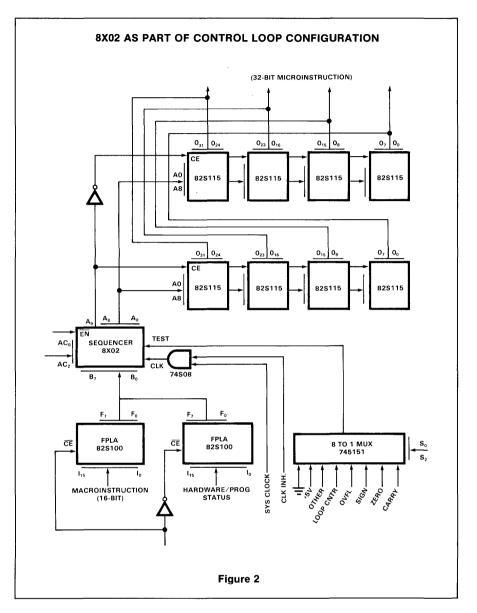

Figure 2 shows an LSI approach to the implementation of the same generalized CPU structure indicated earlier.

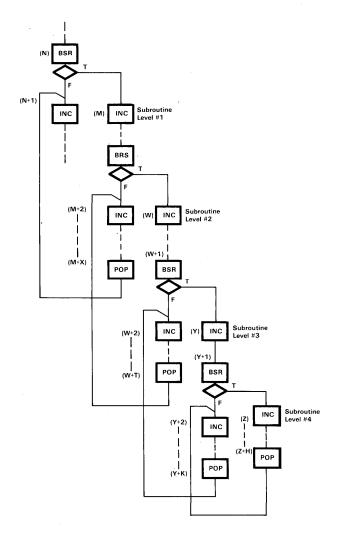

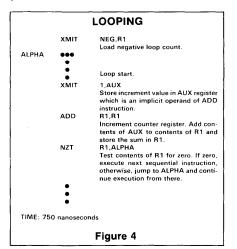

The devices presented in this chapter represent Signetics line of slice microprocessor components. Included is the popular 3000 series Microprogram Control Unit and the 2-bit slice Central Processing Element. These Signetics devices feature improved performance specifications over 3000 series components available on the general market. Moreover, the unique Signetics XL plastic package design results in significantly cooler operation of the chip than was previously possible with other plastic package designs. This section also features the 8X02 Control Store Sequencer. This device may be used with any TTL compatible slice processing elements and features extreme ease of use. The 8 simple, yet powerful, instructions permit subroutining and looping (using internal stack), unrestricted jumping, unrestricted conditional branching and conditional instruction skipping.

8X02-XL,I

#### **DESCRIPTION**

The Signetics 8X02 is a Low-Power Schottky LSI device intended for use in high performance microprogrammed systems to control the fetch sequence of microinstructions. When combined with standard ROM or PROM, the 8X02 forms a powerful microprogrammed control section for computers, controllers, or sequenced logic.

#### **FEATURES**

- Low power Schottky process

- 77ns cycle time (typ)

- 1024 microinstruction addressability

- N-way branch

- 4-level stack register file (LIFO type)

- Automatic push/pop stack operation

- "Test & skip" operation on test input line

- 3-bit command code

- Tri-state buffered outputs

- Auto-reset to address 0 during power-up

- Conditional branching, pop stack, & push stack

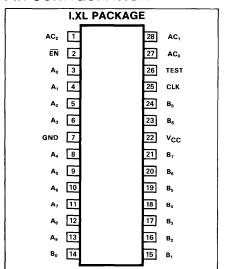

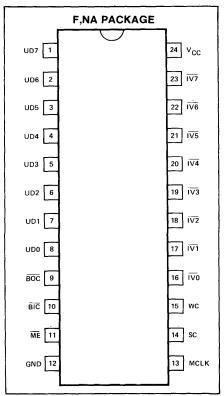

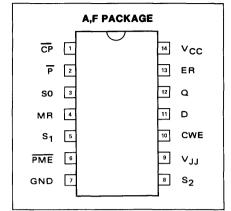

#### **PIN CONFIGURATION**

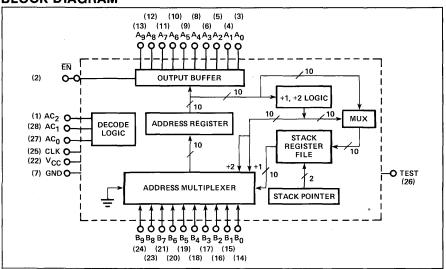

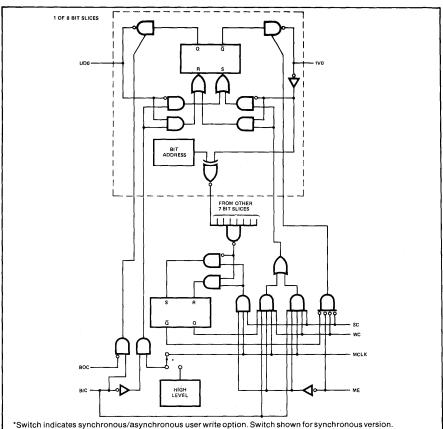

#### **BLOCK DIAGRAM**

#### PIN DESCRIPTION

| PIN            | SYMBOL                           | NAME AND FUNCTION                                                                                                                                                                                                     | TYPE                       |

|----------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 5-6<br>8-13    | $A_0$ - $A_9$                    | Microprogram Address outputs                                                                                                                                                                                          | Three-state<br>Active high |

| 1,28,27        | AC <sub>0</sub> -AC <sub>2</sub> | Next Address Control Function inputs All addressing control functions are selected by these command lines.                                                                                                            | Active high                |

| 14-21<br>23-24 | B <sub>0</sub> -B <sub>9</sub>   | Branch Address inputs Determines the next address of an N-way branch when used with the BRANCH TO SUBROUTINE (BSR) or BRANCH ON TEST (BRT) command.                                                                   | Active high                |

| 2              | ĒN                               | Enable input When in the low state, the Microprogram Address outputs are enabled.                                                                                                                                     | Active low                 |

| 25             | CLK                              | Clock input                                                                                                                                                                                                           |                            |

| 26             | TEST                             | All registers are triggered on the low-to-high transition of the clock.  Test input Used in conjunction with four NEXT ADDRESS CONTROL FUNCTION commands to effect conditional skips, branches, and stack operations. | Active high                |

| 7              | GND                              | Ground                                                                                                                                                                                                                |                            |

| 22             | VCC                              | +5 Volt supply                                                                                                                                                                                                        |                            |

8X02-XL,I

#### **FUNCTIONAL DESCRIPTION**

The Signetics 8X02 Control Store Sequencer is an LSI device using Low Power Schottky technology and is intended for use in high performance microprogrammed applications. When used alone, the 8X02 is capable of addressing up to 1K words of microprogram. This may be expanded to any microprogram size by conventional paging techniques.

The Address Register consists of 10 D-type, edge-triggered flip-flops with a common clock. A new address is entered into the Address Register on the low-to-high transition of the clock. The next address to be entered into the Address Register is supplied via the Address Multiplexer.

The Address Multiplexer is a 5-input device that is used to select either the branch input, +1 adder, +2 adder, stack register file, or ground (all zeros) as the source of the next microinstruction address. The proper multiplexer channel is automatically selected via the Decode Logic according to the Address Control Function Input and Test Input line.

The +1, +2 logic is used to increment the present contents of the Address Register by 1 or 2, depending on the function input command. Thus, the next address to the

Control Store ROM/PROM may be either the current address plus 1 (N+1) or the current address plus 2 (N+2). If the same Microprogram Address is to be used on successive occasions, the clock to the 8X02 must simply be disabled; therefore, no new address is loaded into the Address Register.

The Stack File Register is used to provide a return address linkage whenever a subroutine or loop is executed. The 4X10 stack operates in a last-in, first-out (LIFO) mode, with the stack pointer always pointing to the next address to be read. Operation of the stack pointer is automatically controlled by the Address Control Function Inputs. Since the stack is 4 words deep, up to 4 loops and/or subroutines may be nested.

The branch input is a 10-bit field of direct inputs to the multiplexer which can be selected as the next control store address. Using the appropriate branch command, an N-way branch is possible where N is the address of any microinstruction within the 1024 word microcode page. Likewise, the RESET command is a special case of an N-way branch in which the multiplexer selects an all zeros input, forcing the next microinstruction address to be zero.

The Test Input line is used in conjunction with the conditional execution of 4 Address Control Function commands. When the Test Input is false (low), the sequencer simply increments to the next address (N+1). When it is true (high), the sequencer executes a branch as defined by the input command, thereby transferring control to another portion of the microprogram.

All Address Output lines of the 8X02 are three-state buffered outputs with a common enable line  $(\overline{EN})$ . When the Enable line is high, all outputs are placed in a high-impedance state, and external access to the control store ROM/PROM is possible. This allows a preprogrammed set of microinstructions to be executed from external or built-in test equipment (BITE), vectored interrupts, and Writable Control Store if implemented.

#### **NEXT ADDRESS CONTROL FUNCTION**

| MNEMONIC | DESCRIPTION                                     | FUNCTION<br>AC <sub>2 1 0</sub> | TEST          | NEXT ADDRESS                  | STACK                   | STACK POINTER |

|----------|-------------------------------------------------|---------------------------------|---------------|-------------------------------|-------------------------|---------------|

| TSK      | Test & skip                                     | 000                             | False<br>True | Current + 1<br>Current + 2    | N.C.<br>N.C.            | N.C.<br>N.C.  |

| INC      | Increment                                       | 0 0 1                           | X             | Current + 1                   | N.C.                    | N.C.          |

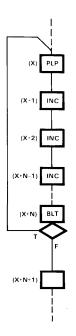

| BLT      | Branch to loop if test input true               | 0 1 0                           | False<br>True | Current + 1<br>Stack reg file | X<br>POP (read)         | Decr<br>Decr  |

| POP      | POP stack                                       | 0 1 1                           | x             | Stack reg file                | POP (read)              | Decr          |

| BSR      | Branch to sub-<br>routine if test<br>input true | 100                             | False<br>True | Current + 1<br>Branch address | N.C.<br>PUSH (Curr + 1) | N.C.<br>Incr  |

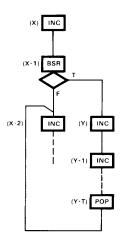

| PLP      | Push for looping                                | 101                             | x             | Current + 1                   | PUSH (Curr Addr)        | Incr          |

| BRT      | Branch if test input true                       | 1 1 0                           | False<br>True | Current + 1<br>Branch address | N.C.<br>N.C.            | N.C.<br>N.C.  |

| RST      | Set microprogram<br>address output to<br>zero   | 1 1 1                           | Х             | All O's                       | N.C.                    | N.C.          |

X = Don't care N.C. = No change

8X02-XL,I

#### **FUNCTIONAL DESCRIPTION**

The following is a description of each of the eight Next Address Control Functions ( $AC_2$ - $AC_0$ )

| MNEMONIC | FUNCTION DESCRIPTION                                                                                                                                                                                                                                                                                                                                                  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSK      | AC <sub>2-0</sub> = 000: TEST & SKIP  Perform test on TEST INPUT LINE.  If test is  Next Address = Current Address + 1  FALSE (LOW):  Stack Pointer unchanged  If test is  Next Address = Current Address + 2  TRUE (HIGH)  (i.e. Skip next microinstruction)  Stack Pointer unchanged                                                                                |

| INC      | AC <sub>2-0</sub> = 001: INCREMENT  Next Address = Current Address + 1  Stack Pointer unchanged                                                                                                                                                                                                                                                                       |

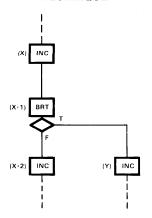

| BLT      | AC <sub>2-0</sub> =010: BRANCHTO LOOP  IF TEST CONDITION TRUE.  Perform test on TEST INPUT LINE.  If test is Next Address = Current Address + 1  FALSE (LOW): Stack Pointer decremented by 1  If test is Next Address = Address from Stack  TRUE (HIGH): Register File (POP)  Stack Pointer decremented by 1                                                          |

| POP      | AC <sub>2-0</sub> = 011: POP STACK  Next Address = Address from Stack Register File (POP)  Stack Pointer decremented by 1                                                                                                                                                                                                                                             |

| BSR      | AC <sub>2-0</sub> = 100: BRANCHTO SUBROUTINE  IF TEST CONDITION TRUE.  Perform test on TEST INPUT LINE.  If test is Next Address = Current Address + 1  FALSE (LOW): Stack Pointer unchanged  If test is Next Address = Branch Address Input (B <sub>0-9</sub> )  TRUE (HIGH): Stack Pointer incremented by 1  PUSH (write) Current Address + 1 → Stack Register File |

| PLP      | AC <sub>2-0</sub> = 101: PUSH FOR LOOPING  Next Address = Current Address + 1  Stack Pointer incremented by 1  PUSH (write) Current Address → Stack Register File                                                                                                                                                                                                     |

| BRT      | AC <sub>2-0</sub> = 110: BRANCH ON TEST CONDITION TRUE Perform test on TEST INPUT LINE. If test is Next Address = Current Address + 1 FALSE (LOW): Stack Pointer unchanged If test is Next Address = Branch Address Input (B <sub>0-9</sub> ) TRUE (HIGH): Stack Pointer unchanged                                                                                    |

| RST      | AC <sub>2-0</sub> = 111: RESET TO ZERO  Next Address = 0  Stack Pointer unchanged                                                                                                                                                                                                                                                                                     |

#### **ABSOLUTE MAXIMUM RATINGS**

|      | PARAMETER                   | RATING        | UNIT |

|------|-----------------------------|---------------|------|

| VCC  | Power supply voltage        | +7            | Vdc  |

| VIN  | Input voltage               | +5.5          | Vdc  |

| VO   | Off-State output voltage    | +5.5          | Vdc  |

| TA   | Operating temperature range | 0° to +70°    | °C   |

| Tstg | Storage temperature range   | -65° to +150° | °C   |

8X02-XL,I

#### DC ELECTRICAL CHARACTERISTICS $0^{\circ}C \leqslant +70^{\circ}C$ , 4.75V, $VCC \leqslant 5.25V$

|                 | PARAMETER                                                                                 | TEST CONDITIONS                                   |     | LIMIT            | S                       | UNIT           |

|-----------------|-------------------------------------------------------------------------------------------|---------------------------------------------------|-----|------------------|-------------------------|----------------|

| PARAMETER       |                                                                                           | TEST CONDITIONS                                   | Min | Typ <sup>1</sup> | Max                     | UNII           |

| VIH             | High level input voltage                                                                  |                                                   | 2   |                  |                         | ٧              |

| VIL             | Low level input voltage                                                                   |                                                   |     | i                | 0.8                     | v              |

| V               | Input clamp voltage                                                                       | V <sub>CC</sub> = 4.75V, I <sub>I</sub> = -18mA   |     |                  | -1.5                    | v              |

| νон             | High level output voltage                                                                 | V <sub>CC</sub> = 4.75V, I <sub>OH</sub> = -2.6mA | 2.4 |                  |                         | V              |

| VOL             | Low level output voltage                                                                  | V <sub>CC</sub> = 4.75V, I <sub>OL</sub> = 8mA    |     |                  | 0.5                     | V              |

| Į,              | Input current at maximum Input voltage                                                    | V <sub>CC</sub> = 5.25V, V <sub>I</sub> = 5.5V    |     |                  | 100                     | μΑ             |

| ΙΉ              | High level input current $AC_2$ - $AC_0$ , $\overrightarrow{EN}$ , TEST $B_9$ - $B_0$ CLK | V <sub>CC</sub> = 5.25V, V <sub>1</sub> = 2.7V    |     |                  | 40<br>20<br>60          | μΑ<br>μΑ<br>μΑ |

| <sup>1</sup> IL | Low level input current $AC_2$ - $AC_0$ , $\overline{EN}$ , $TEST$ $B_9$ - $B_0$ $CLK$    | V <sub>CC</sub> = 5.25V, V <sub>I</sub> = 0.4V    |     |                  | -0.72<br>-0.36<br>-1.08 | mA<br>mA<br>mA |

| los             | Short-circuit output current                                                              | V <sub>CC</sub> = 5.25V                           | -20 |                  | -100                    | mA             |

| lozh            | High-Z state output current                                                               | V <sub>OUT</sub> = 2.7V                           |     |                  | 20                      | μΑ             |

| IOZL            | High-Z state output current                                                               | V <sub>OUT</sub> = 0.4V                           |     |                  | -20                     | μΑ             |

| 1 <sub>CC</sub> | Supply current                                                                            | V <sub>CC</sub> = 5.25V                           |     | 130              | 155                     | mA             |

1. All typical values are at  $V_{CC}$  = 5V,  $T_A$  = 25°C.

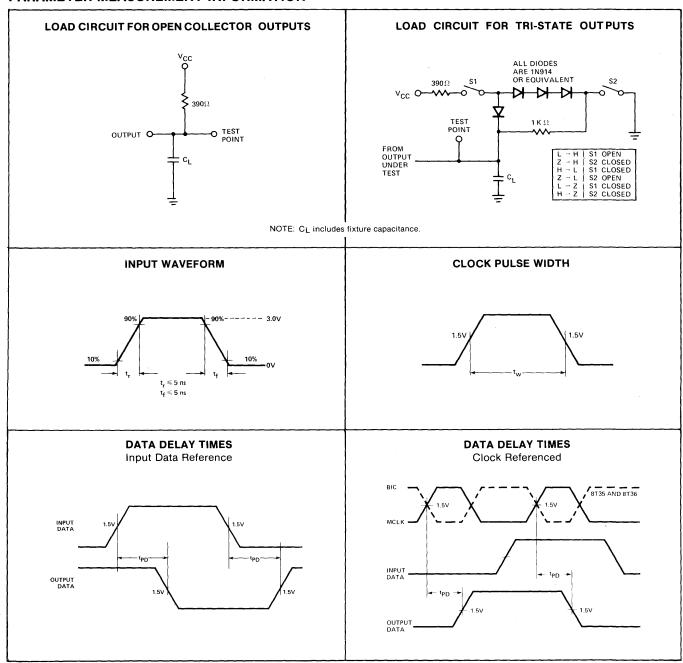

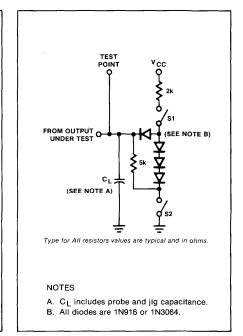

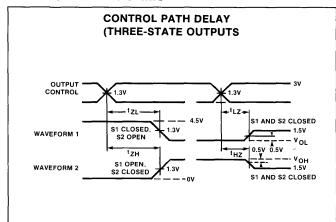

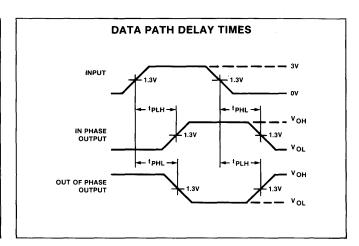

#### PARAMETER MEASUREMENT INFORMATION

#### NOTES

- A. C  $_{L}$  includes probe and jig capacitance. B. All diodes are 1N916 or 1N3064. C. R  $_{L}$  = 2k, C = 15pF.

#### AC ELECTRICAL CHARACTERISTICS TA = $0^{\circ}$ C to $+70^{\circ}$ C, VCC = 5.0V ± 5%

| PARAMETER        |                        | FROM          | то                               |     | LIMITS   |     | LINIT    |

|------------------|------------------------|---------------|----------------------------------|-----|----------|-----|----------|

|                  | PARAMETER              | INPUT         | OUTPUT                           | Min | Typ¹     | Max | UNIT     |

| t <sub>cy</sub>  | Cycle time             |               |                                  |     | 77       |     | ns       |

| tpw              | Clock pulse width high |               |                                  |     | 32       | ļ   | ns       |

| tpw              | Clock pulse width low  |               |                                  | 1   | 45       | 1   | ns       |

| Enable           | delay                  |               |                                  |     |          |     |          |

| $t_{PLZ}$        | Low-to-high-Z          |               |                                  | } } | 12       | }   | ns       |

| tPHZ             | High-to-high-Z         | EN            | $A_9 - A_0$                      |     | 16       |     | ns       |

| <sup>t</sup> PZL | High-Z-to-low          |               |                                  |     | 14       | ]   | ns       |

| t <sub>PZH</sub> | High-Z-to-high         |               |                                  |     | 8        |     | ns       |

|                  | ation Delay            |               |                                  |     |          | ] [ |          |

| t <sub>PHL</sub> | High-to-low            | OL K          | Λ Λ                              | iii | 32       | 1 1 |          |

| t <sub>PLH</sub> | Low-to-high            | CLK           | $A_9$ - $A_0$                    |     | 20       | 1   | ns       |

|                  | and Hold times         |               |                                  | 1 1 |          | 1 1 |          |

|                  | spect to CLK (1)       |               |                                  |     |          |     |          |

| tsF              | Set-up time high       | Control, Data | AC <sub>2</sub> -AC <sub>0</sub> |     | 70       |     | ns       |

| t <sub>HF</sub>  | Hold time high         | 22            | 2 0                              |     | -6       |     | ns       |

|                  | Set-up time high       | Control, Data | $B_9$ - $B_0$                    |     | 22       | ) ] | ns       |

| t <sub>SF</sub>  | Hold time high         | Control, Data | Dg D0                            |     | -15      |     | ns       |

| tHF              | •                      | 0 5 .         | Tank                             |     |          |     | •        |

| <sup>t</sup> SI  | Set-up time high       | Control, Data | Test                             |     | 70<br>-6 |     | ns       |

| <sup>t</sup> HI  | Hold time high         |               | _                                |     |          |     | ns       |

| t <sub>SF</sub>  | Set-up time low        | Control, Data | $AC_2$ - $AC_0$                  |     | 70       |     | ns       |

| <sup>t</sup> HF  | Hold time low          |               |                                  |     | 8        |     | ns       |

| <sup>t</sup> sk  | Set-up time low        | Control, Data | $B_9$ - $B_0$                    |     | 24       |     | ns       |

| <sup>t</sup> HK  | Hold time low          |               |                                  |     | -14      | }   | ns       |

| tsı              | Set-up time low        | Control, Data | Test                             |     | 70       |     | ns       |

| t <sub>HI</sub>  | Hold time low          | John on, Bata |                                  |     | 8        |     | ns       |

|                  | Set-up time high       | Function      | BRT/BSR                          |     | 50       |     | ns       |

| ts<br>to         | Set-up time low        | Tanction      | BITT/BOTT                        |     | 37       | 1 1 | ns       |

| t <sub>S</sub>   | •                      | F             | TSK                              |     | 52       |     |          |

| ts               | Set-up time high       | Function      | 151                              | 1   | 70       |     | ns<br>ns |

| ts               | Set-up time low        |               |                                  |     |          |     |          |

| ts               | Set-up time high       | Function      | INC                              |     | 32       |     | ns       |

| ts               | Set-up time high       | Function      | RST                              |     | 27       |     | ns       |

| tS               | Set-up time high       | Function      | POP/BLT                          |     | 70       | ]   | ns       |

|                  | spect to CLK (↓)       |               |                                  |     |          |     |          |

| tSF              | Set-up time high       | Control, Data | AC <sub>2</sub> -AC <sub>0</sub> |     | 23       |     | ns       |

| tsı              | Set-up time high       | Control, Data | Test                             |     | 23       | 1   | ns       |

| <sup>t</sup> SF  | Set-up time low        | Control, Data | AC <sub>2</sub> -AC <sub>0</sub> |     | 22       | [   | ns       |

| <sup>t</sup> SI  | Set-up time low        | Control, Data | Test                             |     | 22       |     | ns       |

NOTE

<sup>1.</sup> Typical values are for TA = 25°C, VCC = 5.0V.

#### **VOLTAGE WAVEFORMS**

19

#### INTRODUCTION

The introduction of the Signetics Series 3000 Bipolar Microprocessor Chip Set has brought new levels of high performance to microprocessor applications not previously possible with MOS technology. Combining the Schottky bipolar N3001 Microprogram Control Unit (MCU) and N3002 Central Processing Element (CPE) with industry standard memory and support circuits, microinstruction cycle times of 100ns are possible.

In the majority of cases, the choice of a bipolar microprocessor slice, as opposed to an MOS device, is based on speed or flexibility of microprogramming. Starting with these characteristics, the design of the Signetics Series 3000 Microprocessor has been optimized around the following objectives:

- · Fast cycle time

- All memory and support chips are industry standard

- Cooler operation

- Lower total system cost

Furthermore, systems built with large-scale integrated circuits are much smaller and require less power than equivalent systems using medium and/or small scale integrated circuits.

The 2 components of the Series 3000 chip set, when combined with industry standard memory and peripheral circuits, allows the design engineer to construct highperformance processors and/or controllers with a minimum amount of auxillary logic. Features such as the multiple independent address and data buses, tri-state logic, and separate output enable lines eliminate the need for time-multiplexing of buses and associated hardware.

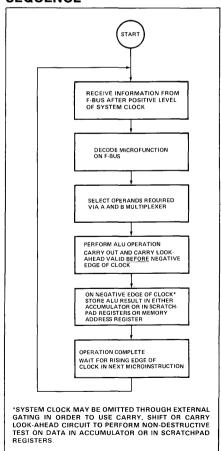

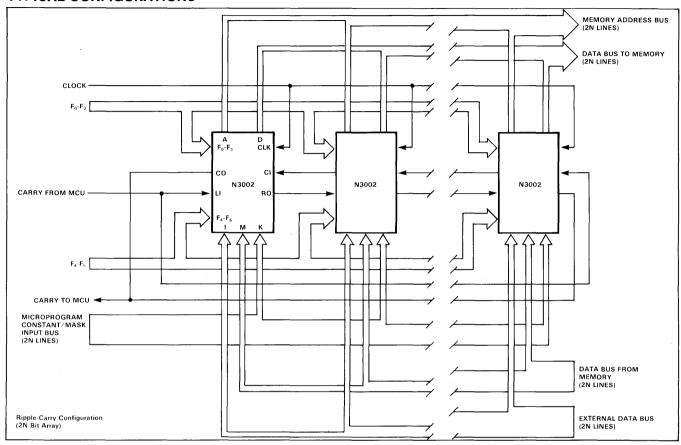

Each Central Processing Element represents a complete 2-bit slice through the data processing section of a computer. Several CPEs may be connected in parallel to form a processor of any desired word length. The Microprogram Control Unit controls the sequence in which microinstructions are fetched from the microprogram memory (ROM/PROM), with these microinstructions controlling the step-by-step operation of the processor.

Each CPE contains a 2-bit slice of 5 independent buses. Although they can be used in a variety of ways, typical connections are:

Input M-bus: Carries data from external

memory

Input I-bus: Carries data from input/output

device

Input K-bus: Used for microprogram mask or

> literal (constant) value input Connected to CPE Memory

Output A-bus: Address Register

Output D-bus: Connected to CPE accumulator.

As the CPEs are paralleled together, all buses, data paths, and registers are correspondingly expanded.

The microfunction input bus (F-bus) con-

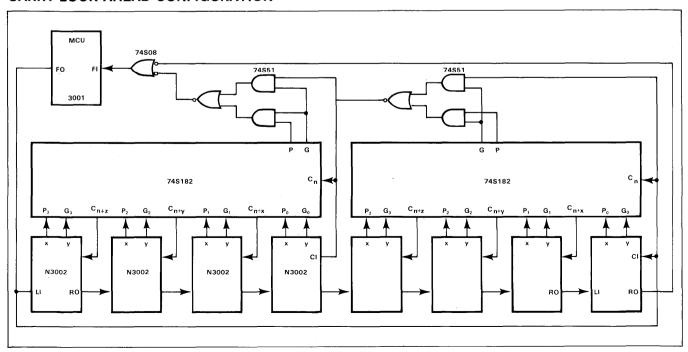

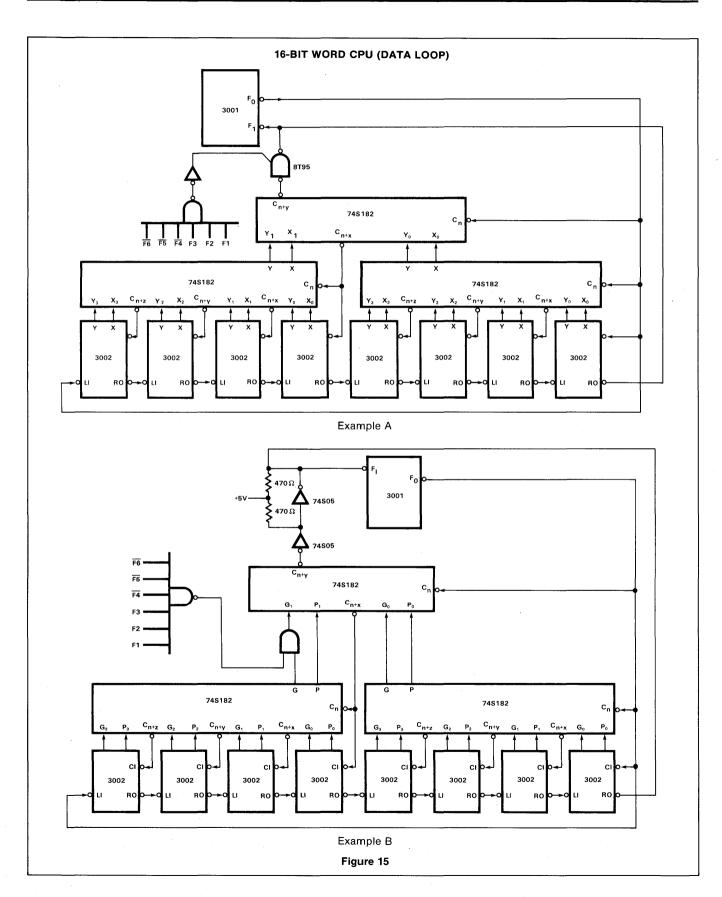

trols the internal operation of the CPE, selecting both the operands and the operation to be executed upon them. The arithmetic logic unit (ALU), controlled by the microfunction decoder, is capable of over 40 Boolean and binary operations as outlined in the Function Description section of the N3002 data sheet. Standard carry look-ahead outputs (X and Y) are generated by the CPE for use with industry standard devices such as the 74S182.

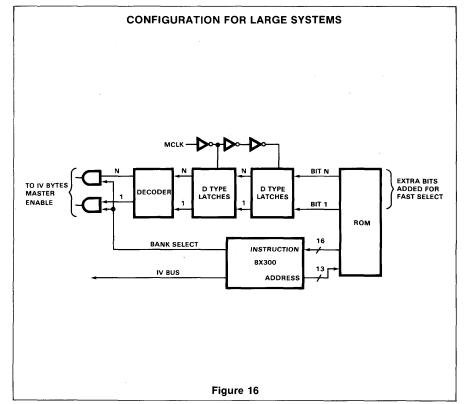

A typical processor configuration is shown in Figure 1. It should be remembered that in working with slice-oriented microprocessors, the final configuration may be varied to enhance speed, reduce component count, or increase data-processing capability. One method of maximizing a processor's performance is called pipelining. To accomplish this, a group of D-type flip-flops or latches (such as the 74174 Hex D-type Flip-Flop) are connected to the microprogram memory outputs (excluding the address control field AC<sub>0</sub>-AC<sub>6</sub>) to buffer the current microinstruction and allow the MCU to overlap the fetch of the next instruction with the execution of the current one. The time saved in pipelining operations is the shorter of either the address set-up time to the microprogram memory (ROM/PROM) or the access time of the ROM/PROM. A convenient way of implementing pipelining is to use ROMs with on-board latches, such as the Signetics 82S115.

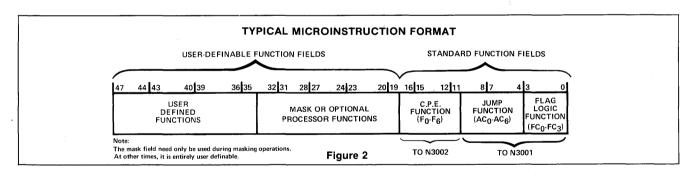

Figure 2 shows a typical microinstruction format using the 82S114 PROMs contained in the Signetics 3000 Microprocessor Designer's Evaluation Kit. Although this particular example is for a 48-bit word (6 PROMs), the allocation of bits for the mask (K-bus) and optional processor functions depends on the specific application of the system and the trade offs which the designer wishes to make

In using the K-bus, it should be kept in mind that the K inputs are always ANDed with the B-multiplexer outputs into the ALU. Bit masking, frequently done in computer control systems, can be performed with the mask supplied to the K-bus directly from the microinstruction.

By placing the K-bus in either the all-one or all-zero condition (done with a single control bit in the microinstruction), the accumulator will either be selected or deselected, respectively, in a given operation. This feature nearly doubles the amount of microfunctions in the CPE. A description of these various microfunctions can be found in the N3002 data sheet under the heading Function Description by referring to the K-bus conditions of all-ones (11) and all-zeros (00).

The MCU controls the sequence in which microinstructions are fetched from the mi-

croprogram memory (ROM/PROM). In its classical form, the MCU would use a nextaddress field in each microinstruction. However, the N3001 uses a modified classical approach in which the microinstruction field specifies conditional tests on the MCU bus inputs and registers. The next-address logic of the MCU also makes extensive use of a row/column addressing scheme, whereby the next address is defined by a 5bit row address and 4-bit column address. Thus, from a particular address location, it is possible to jump unconditionally to any location within that row or column, or conditionally to other specified locations in one operation. Using this method, the processor functions can be executed in parallel with program branches.

As an example of this flexibility, let us assume a disk controller is being designed. As part of the sequence logic, 3 bits of the disk drive status word must be tested and all 3 must be true in order to proceed with the particular sequencing operation. In any sequencing operation using a status word for conditional branch information, there are innumerable combinations of bits which must be tested throughout the sequencing operation. Using discrete logic techniques, this would involve several levels of gating. However, the entire operation can be done in two microinstructions. First, the mask (K-

bus) field in the microinstruction format is encoded with a one for each corresponding status bit to be tested and a zero for each bit to be discarded. The status word is input via the I-bus and ANDed with the K-bus mask using the CPE microfunction operation from F-Group 2, R-Group III. Assuming we are using low-true logic (true = 0 volts). we now test the result, which is located in the accumulator AC, for all zeros using the CPE microfunction operation from F-Group 5, R-Group III. Depending on the zero/nonzero status of AC, a one or zero will be loaded into the carryout CO bit. This bit can now be used as a condition for the next address jump calculation within the N3001 MCU. If the AC was zero (status word was true), we will jump to the next address within our controller sequence. If the AC was nonzero (status word not true), then a jump would be made back to the beginning of this 2-microinstruction loop and the test sequence repeated until the status word (all 3 bits) is true.

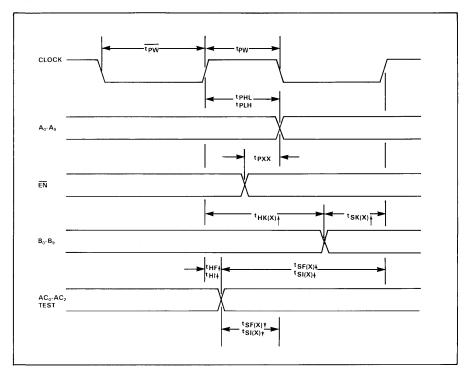

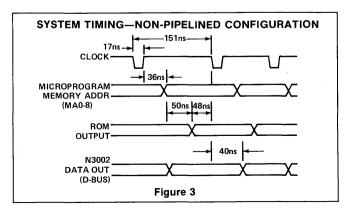

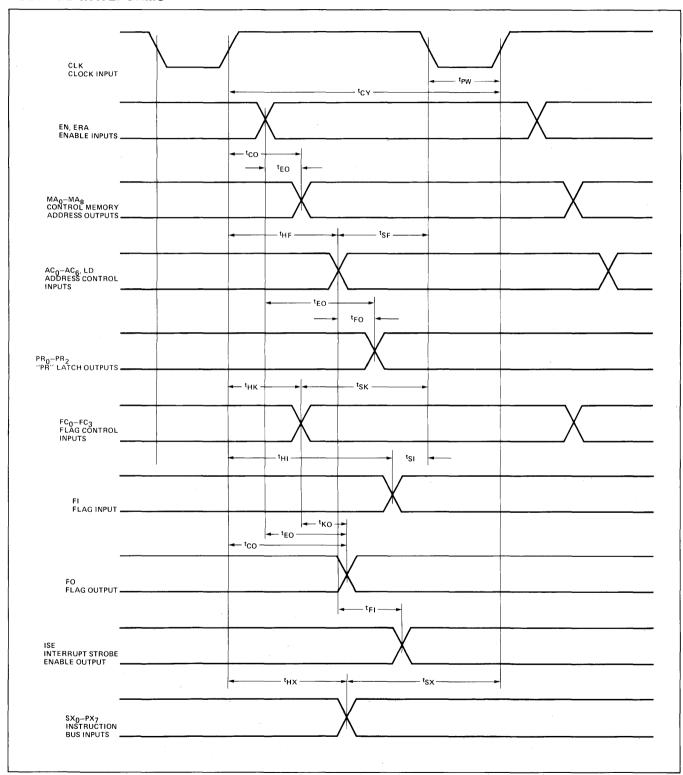

Figure 3 shows a typical timing diagram for a system operating in the non-pipelined mode. Keep in mind that the maximum clock rate is dependent upon the total of propagation delay times plus required setup times. It is at the designer's discretion to resolve the speed versus complexity tradeoffs.

#### **ABSOLUTE MAXIMUM RATINGS\***

|                                | N3001/N3002     | S3001/S3002     |

|--------------------------------|-----------------|-----------------|

| Temperature under bias         | 0°C to +70°C    | -55°C to +125°C |

| Storage temperature            | -60°C to +160°C | -65°C to +150°C |

| All output and supply voltages | -0.5V to +7V    | -0.5V to +7V    |

| All input voltages             | -1.0V to +5.5V  | -1.0V to +5.5V  |

| Output currents                | 100mA           | 100mA           |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the  $\ \, \text{device. This is a stress rating only and functional operation of the device at these or any other conditions}$  $above\ those\ indicated\ in\ the\ operational\ sections\ of\ the\ specification\ is\ not\ implied.\ Exposure\ to\ absolute$ maximum ratings for extended periods may effect device reliability.

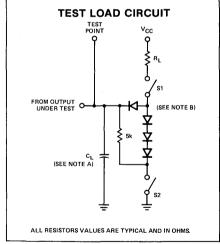

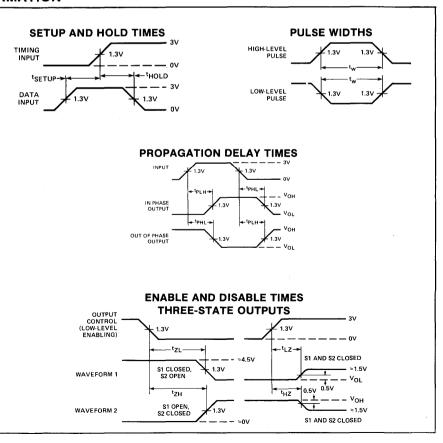

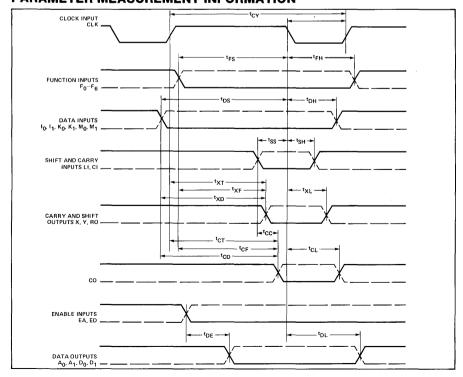

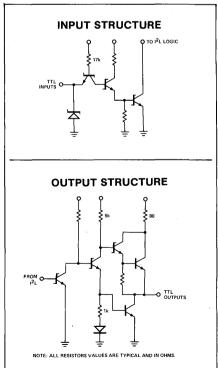

#### PARAMETER MEASUREMENT **INFORMATION**

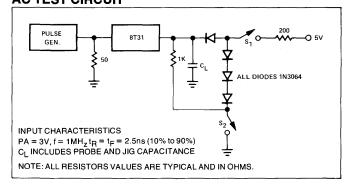

NOTE: All resistor values are typical and in ohms.

NOTE: All resistor values are typical and in ohms. TEST CONDITIONS: Input pulse amplitude of 2.5 volts Input rise and fall times of 5ns between 1 volt and 2 volts Output load of 10mA and 50pF Speed measurements are taken at the 1.5 volt level

N3001/N3002  $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$

#### DC ELECTRICAL CHARACTERISTICS \$3001/\$3002 T<sub>A</sub> = -55°C to +125°C

|                    | D.D.444575D                                                                    | TEGT CONDITIONS                                                                                                                                                                                                   | N3          | 001/N30                 | 02                                         | S        | 3001/\$30                           | 002                                             |                            |

|--------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------|--------------------------------------------|----------|-------------------------------------|-------------------------------------------------|----------------------------|

|                    | PARAMETER                                                                      | TEST CONDITIONS                                                                                                                                                                                                   | Min Typ Max |                         | Max                                        | Min      | Тур                                 | Max                                             | UNIT                       |

| VIL<br>VIH<br>VIC  | Low level input voltage<br>High level input voltage<br>Input clamp voltage     | V <sub>CC</sub> = 5.0V<br>V <sub>CC</sub> = 5.0V<br>V <sub>CC</sub> = 4.75V, I <sub>C</sub> = -5mA                                                                                                                | 2.0         | -0.55                   | 0.8<br>-1.0                                | 2.0      | -0.8                                | 0.8                                             | V<br>V<br>V                |

|                    | Low level output voltage<br>High level output voltage                          | V <sub>CC</sub> = 4.75V, I <sub>OL</sub> =10mA<br>V <sub>CC</sub> = 4.75V, I <sub>OH</sub> = -1mA<br>mA <sub>0</sub> - mA <sub>8</sub> , ISE, FO                                                                  |             | 0.35<br>2.4             | 0.45<br>3.0                                |          | 0.35<br>2.4                         | 0.45<br>3.0                                     | V<br>V                     |

| I <sub>F</sub>     | Input load current N3001 Input leakage current N3001                           | V <sub>CC</sub> = 5.25V, V <sub>F</sub> = 0.45V<br>CLK input<br>EN input<br>All other inputs<br>V <sub>CC</sub> = 5.25V, V <sub>R</sub> = 5.25V<br>CLK input<br>EN input<br>All other inputs                      | ,           | -0.21<br>-0.12<br>-0.05 | -0.75<br>-0.50<br>-0.25<br>120<br>80<br>40 | \        | -0.21<br>-0.12<br>-0.05<br>/R = 5.5 | -0.75<br>-0.50<br>-0.25<br>V<br>120<br>80<br>40 | mA<br>mA<br>mA<br>μA<br>μA |

| IOS<br>IO<br>(off) | Short circuit output current  Off-state output current                         | $V_{CC} = 5.0V$ $mA_0 - mA_8$ , ISE, FO $V_{CC} = 5.25V$ $PR_0 - PR_2$ , $mA_0 - mA_2$ , FO $V_{OUT} = 0.45V$ $mA_0 - mA_8$ , FO $V_{OUT} = 5.25V$                                                                | -15         | -28                     | -60<br>-100<br>+100                        | -15<br>V | -28<br>OUT = 5                      | -60<br>  -100<br>  5.5V<br>  +100               | mΑ<br>μΑ<br>μΑ             |

| ICC                | Power supply current N3001 Power supply current N3002 Input Load Current N3002 | $V_{CC} = 5.25V^2$ $V_{CC} = 5.25V, V_F = 0.45v$                                                                                                                                                                  |             | 170<br>145              | 240<br>190                                 |          | 170<br>145                          | 250<br>210                                      | mA                         |

| 'F                 |                                                                                | F <sub>0</sub> -F <sub>6</sub> , CLK, K <sub>0</sub> , K <sub>1</sub> , EA, ED<br>I <sub>0</sub> , I <sub>1</sub> , M <sub>0</sub> , M <sub>1</sub> , LI<br>CI                                                    |             | -0.05<br>-0.85<br>-2.3  | -0.25<br>-1.5<br>-4.0                      |          | -0.05<br>-0.85<br>-2.3              | -0.25<br>-1.5<br>-4.0                           | mA<br>mA<br>mA             |

| I <sub>R</sub>     | Input Leakage Current N3002                                                    | V <sub>CC</sub> = 5.25V, V <sub>R</sub> = 5.25V<br>F <sub>0</sub> -F <sub>6</sub> , CLK, K <sub>0</sub> , K <sub>1</sub> , EA, ED<br>I <sub>0</sub> , I <sub>1</sub> , M <sub>0</sub> , M <sub>1</sub> , LI<br>CI |             |                         | 40<br>60<br>180                            |          |                                     | 40<br>60<br>180                                 | μΑ<br>μΑ<br>μΑ             |

#### NOTES

<sup>1.</sup> SN3001 typical values are for T  $_{A}$  = 25°C, V  $_{CC}$  = 5.0V 2. SN3002 EN input grounded, all other inputs and outputs open.

SN3002 CLK input grounded, other inputs open.

#### **DESCRIPTION**

The N3001 MCU is 1 element of a bipolar microcomputer set. When used with the S/N3002, 54/74S182, ROM or PROM memory, a powerful microprogrammed computer can be implemented.

The 3001 MCU controls the fetch sequence of microinstructions from the microprogram memory. Functions performed by the 3001 include:

- · Maintenance of microprogram address register

- · Selection of next microinstruction address

- Decoding and testing of data supplied via several input buses

- Saving and testing of carry output data from the central processing (CP) array

- Control of carry/shift input data to the CP array

- Control of microprogram interrupts

#### **FEATURES**

- Schottky TTL process

- 45ns cycle time (typ.)

- Direct addressing of standard bipolar PROM or ROM

- 512 microinstruction addressability

- · Advanced organization:

- 9-bit microprogram address register and bus organized to address memory by row and column

- 4-bit program latch

- 2-flag registers

- 11 address control functions:

- 3 jump and test latch function

- 16 way jump and test instruction

- 8 flag control functions:

- 4 flag input functions

- 4 flag output functions

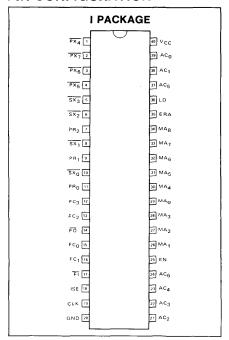

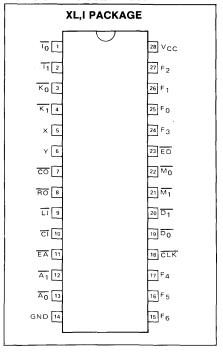

#### PIN CONFIGURATION

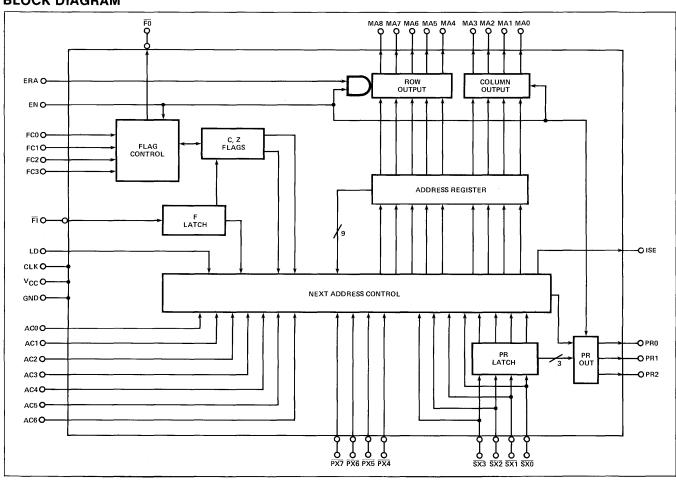

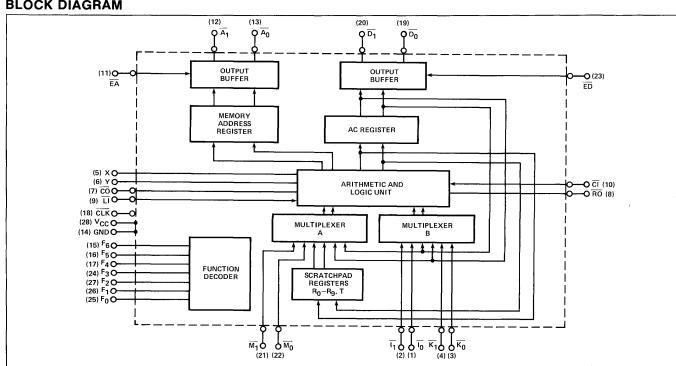

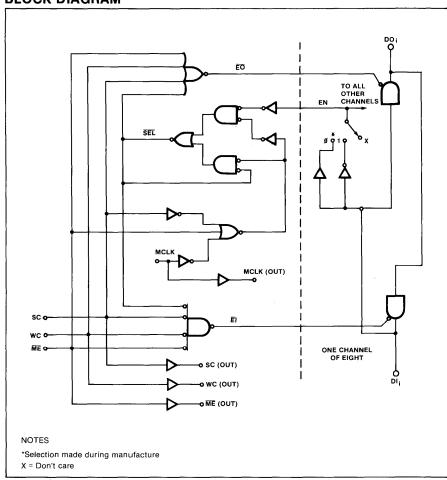

#### **BLOCK DIAGRAM**

#### **PIN DESCRIPTION**

| PIN      | SYMBOL                                | NAME AND FUNCTION                                                                              | TYPE             |

|----------|---------------------------------------|------------------------------------------------------------------------------------------------|------------------|

| 1-4      | $\overline{PX}_4-\overline{PX}_7$     | Primary Instruction Bus Inputs                                                                 | Active low       |

| i        | , ,                                   | Data on the primary instruction bus is tested by the JPX function to                           |                  |

|          |                                       | determine the next microprogram address.                                                       |                  |

| 5,6,8,10 | $\overline{SX}_0$ - $\overline{SX}_3$ | Secondary Instruction Bus Inputs                                                               | Active low       |

|          |                                       | Data on the secondary instruction bus is synchronously loaded into the                         |                  |

|          |                                       | PR-latch while the data on the PX-bus is being tested (JPX). During a                          |                  |

| 1        |                                       | subsequent cycle, the contents of the PR-latch may be tested by the JPR,                       |                  |

|          |                                       | JLL, or JRL functions to determine the next microprogram address.                              |                  |

| 7,9,11   | PR <sub>0</sub> -PR <sub>2</sub>      | PR-Latch Outputs                                                                               | Open Collector   |

|          |                                       | The PR-latch outputs $(SX_0-SX_2)$ are synchronously enabled by the JCE function.              |                  |

|          |                                       | They can be used to modify microinstructions at the outputs of the                             |                  |

|          |                                       | microprogram memory or to provide additional control lines.                                    |                  |

| 12,13    | FC <sub>0</sub> -FC <sub>3</sub>      | Flag Logic Control Inputs                                                                      | Active high      |

| 15,16    | · [                                   | The flat logic control inputs are used to cross-switch the flags (C and Z)                     |                  |

|          |                                       | with the flag logic input (FI) and the flag logic output (FO).                                 |                  |

| 14       | FO                                    | Flag Logic Output                                                                              | Active low       |

|          |                                       | The outputs of the flags (C and Z) are multiplexed internally to form the                      | Three-state      |

|          |                                       | common flag logic output. The output may also be forced to a logical                           |                  |

|          |                                       | 0 or logical 1.                                                                                |                  |

| 17       | FĪ                                    | Flag Logic Input                                                                               | Active low       |

|          |                                       | The flag logic input is demultiplexed internally and applied to the inputs                     |                  |

| i        |                                       | of the flags (C and Z). Note: The flag input data is saved in the F-latch                      |                  |

| l        |                                       | when the clock input (CLK) is low.                                                             |                  |

| 18       | ISE                                   | Interrupt Strobe Enable Output                                                                 | Active high      |

|          |                                       | The interrupt strobe enable output goes to logical 1 when one of the                           |                  |

|          |                                       | JZR functions are selected (see Functional Description). It can be used                        |                  |

|          |                                       | to provide the strobe signal required by interrupt circuits.                                   | 1                |

| 19       | CLK                                   | Clock Input                                                                                    |                  |

| 20       | GND                                   | Ground                                                                                         |                  |

| 21-24    | AC <sub>0</sub> -AC <sub>6</sub>      | Next Address Control Function Inputs                                                           | Active high      |

| 37-39    |                                       | All jump functions are selected by these control lines.                                        |                  |

| 25       | EN                                    | Enable Input                                                                                   |                  |

|          | •                                     | When in the high state, the enable input enables the microprogram                              |                  |

|          |                                       | address, PR-latch and flag outputs.                                                            |                  |

| 26-29    | MA <sub>0</sub> -MA <sub>3</sub>      | Microprogram Column Address Outputs                                                            | Three-state      |

| 30-34    | MA <sub>4</sub> -MA <sub>8</sub>      | Microprogram Row Address Outputs                                                               | Three-state      |

| 35       | ERA                                   | Enable Row Address Input                                                                       | Active high      |

|          |                                       | When in the low state, the enable row address input independently                              |                  |

| ļ        |                                       | disables the microprogram row address outputs. It can be used to facilitate                    | 1                |

| 00       |                                       | the implementation of priority interrupt systems.                                              | A saling to both |

| 36       | LD                                    | Microprogram Address Load Input                                                                | Active high      |

|          |                                       | When the active high state, the microprogram address load input inhibits                       |                  |

| ļ        |                                       | all jump functions and synchronously loads the data on the instruction                         | 1                |

|          | b                                     | buses into the microprogram address register. However, it does not inhibit                     |                  |

| 40       | V                                     | the operation of the PR-latch or the generation of the interrupt strobe enable. +5 Volt supply |                  |

| 70       | v <sub>CC</sub>                       | voit supply                                                                                    |                  |

#### THEORY OF OPERATION

The MCU controls the sequence of microinstructions in the microprogram memory. The MCU simultaneously controls 2 flipflops (C, Z) which are interactive with the carry-in and carry-out logic of an array of CPEs.

The functional control of the MCU provides both unconditional jumps to new memory locations and jumps which are dependent on the state of MCU flags or the state of the "PR" latch. Each instruction has a "jump set" associated with it. This "jump set" is the total group of memory locations which can be addressed by that instruction.

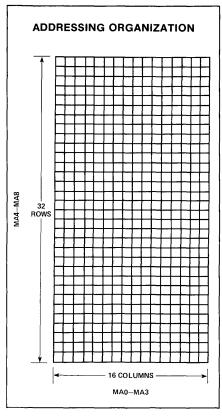

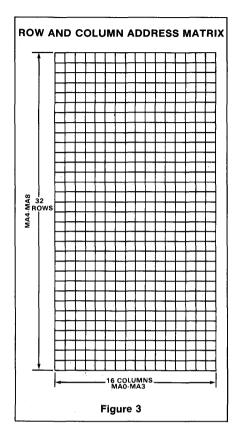

The MCU utilizes a two-dimensional addressing scheme in the microprogram memory. Microprogram memory is organized as 32 rows and 16 columns for a total of 512 words. Word length is variable according to application. Address is accomplished by a 9-bit address organized as a 5-bit row and 4-bit column address.

#### **FUNCTIONAL DESCRIPTION**

The following is a description of each of the eleven address control functions. The symbols shown below are used to specify row and column addresses.

| SYMBOL           | MEANING                                                          |

|------------------|------------------------------------------------------------------|

| row <sub>n</sub> | 5-bit next row address where n is the decimal row address.       |

| coln             | 4-bit next column address where n is the decimal column address. |

#### Unconditional Address Control (Jump) Functions

The jump functions use the current microprogram address (i.e., the contents of the microprogram address register prior to the rising edge of the clock) and several bits from the address control inputs (AC0-AC6) to generate the next microprogram address.

#### Flag Conditional Address Control (Jump Test) Functions

The jump/test flag functions use the current microprogram address, the contents of the selected flag or latch, and several bits from the address control function to generate the next microprogram address.

#### **JUMP FUNCTION TABLE**

| MNEMONIC | FUNCTION DESCRIPTION                                                                                                                                                                                                                                                                                          |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

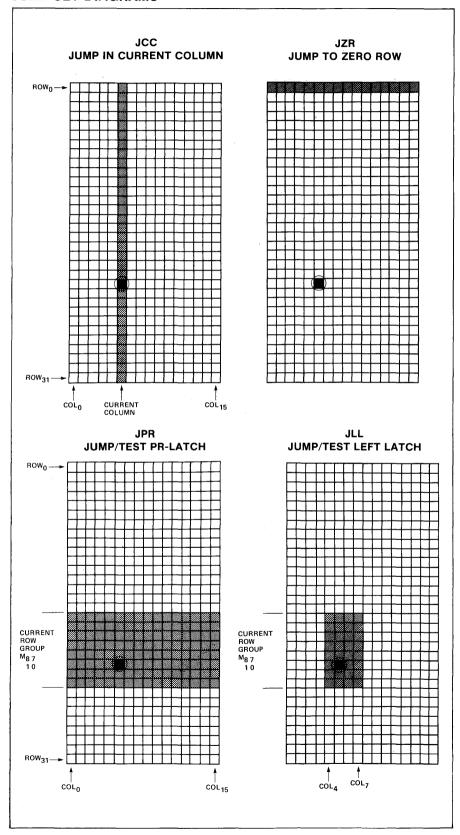

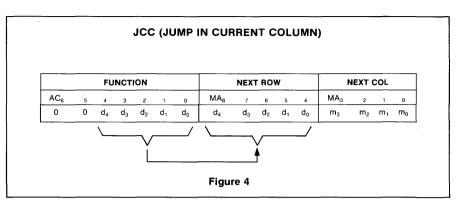

| JCC      | Jump in current column. $AC_0$ - $AC_4$ are used to select 1 of 32 row addresses in the current column, specified by $MA_0$ - $MA_3$ , as the next address.                                                                                                                                                   |

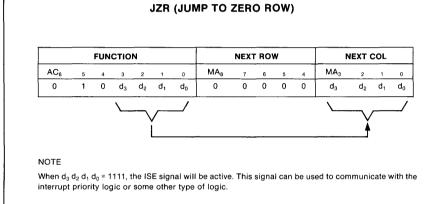

| JZR      | Jump to zero row. $AC_0$ - $AC_3$ are used to select 1 of 16 column addresses in row <sub>0</sub> , as the next address.                                                                                                                                                                                      |

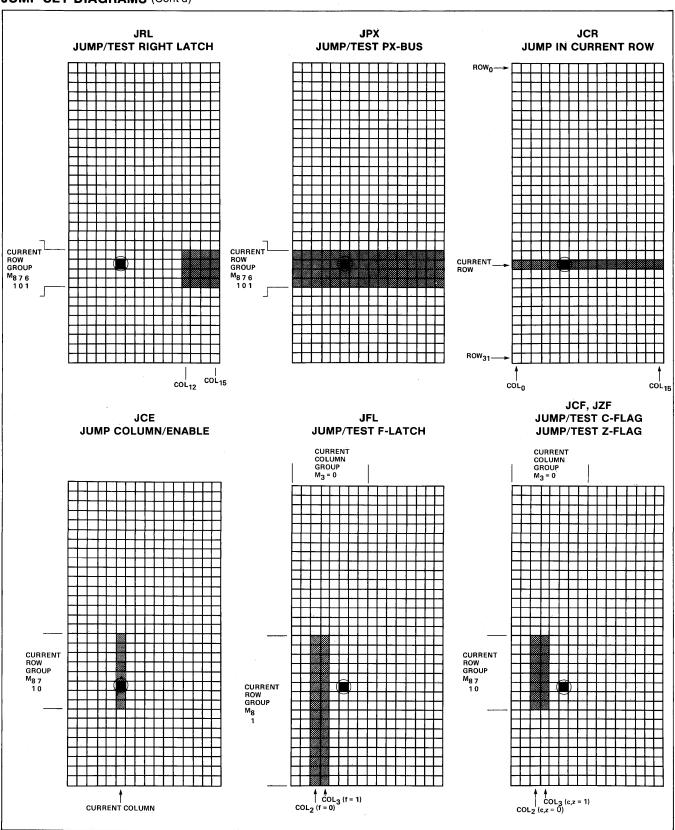

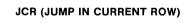

| JCR      | Jump in current row. $AC_0$ - $AC_3$ are used to select 1 of 16 addresses in the current row, specified by $MA_4$ - $MA_8$ , as the next address.                                                                                                                                                             |

| JCE      | Jump in current column/row group and enable PR-latch outputs. $AC_0$ - $AC_2$ are used to select 1 of 8 row addresses in the current row group, specified by $MA_7$ - $MA_8$ , as the next row address. The current column is specified by $MA_0$ - $MA_3$ . The PR-latch outputs are asynchronously enabled. |

#### **JUMP/TEST FUNCTION TABLE**

| MNEMONIC | FUNCTION DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

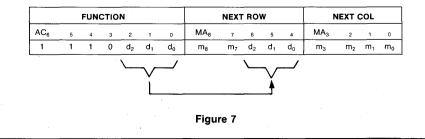

| JFL      | Jump/test F-latch. $AC_0$ - $AC_3$ are used to select 1 of 16 row addresses in the current row group, specified by $MA_8$ , as the next row address. If the current column group, specified by $MA_3$ , is $col_0$ - $col_7$ , the F-latch is used to select $col_2$ or $col_3$ as the next column address. If $MA_3$ specifies column group $col_8$ - $col_{15}$ , the F-latch is used to select $col_{10}$ or $col_{11}$ as the next column address.     |

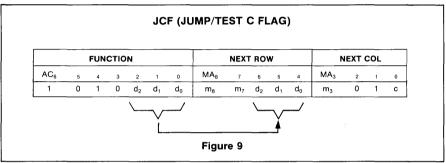

| JCF      | Jump/test C-flag. $AC_0$ - $AC_2$ are used to select 1 of 8 row addresses in the current row group, specified by $MA_7$ and $MA_8$ , as the next row address. If the current column group specified by $MA_3$ is $col_0$ - $col_7$ , the C-flag is used to select $col_2$ or $col_3$ as the next column address. If $MA_3$ specifies column group $col_8$ - $col_{15}$ , the C-flag is used to select $col_{10}$ or $col_{11}$ as the next column address. |

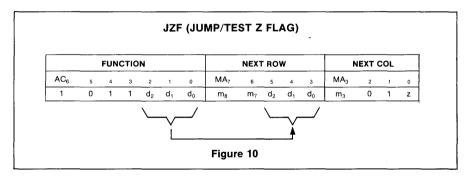

| JZF      | Jump/test Z-flag. Identical to the JCF function described above, except that the Z-flag, rather than the C-flag, is used to select the next column address.                                                                                                                                                                                                                                                                                                |

| JPR      | Jump/test PR-latch. $AC_0$ - $AC_2$ are used to select 1 of 8 row addresses in the current row group, specified by $MA_7$ and $MA_8$ , as the next row address. The 4 PR-latch bits are used to select 1 of 16 possible column addresses as the next column address.                                                                                                                                                                                       |

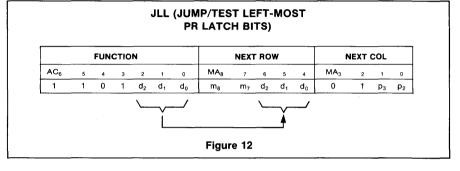

| JLL      | Jump/test leftmost PR-latch bits. $AC_0$ - $AC_2$ are used to select 1 of 8 row addresses in the current row group, specified by $MA_7$ and $MA_8$ , as the next row address. $PR_2$ and $PR_3$ are used to select 1 of 4 column addresses in $col_4$ through $col_7$ as the next column address.                                                                                                                                                          |

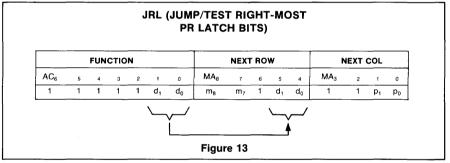

| JRL      | Jump/test rightmost PR-latch bits. $AC_0$ and $AC_1$ are used to select 1 of 4 high-order row addresses in the current row group, specified by $MA_7$ and $MA_8$ , as the next row address. $PR_0$ and $PR_1$ are used to select 1 of 4 possible column addresses in $col_{12}$ through $col_{16}$ as the next column address.                                                                                                                             |

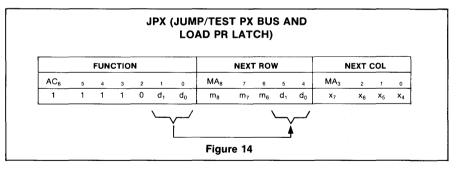

| JPX      | Jump/test PX-bus and load PR-latch. $AC_0$ and $AC_1$ are used to select 1 of 4 row addresses in the current row group, specified by $MA_6$ - $MA_8$ , as the next row address. $PX_4$ - $PX_7$ are used to select 1 of 16 possible column addresses as the next column address. $SX_0$ - $SX_3$ data is locked in the PR-latch at the rising edge of the clock.                                                                                           |

#### PX-Bus and PR-Latch Conditional Address Control (Jump/Test) Functions

The PX-bus jump/test function uses the data on the primary instruction bus (PX<sub>4</sub>-PX<sub>7</sub>), the current microprogram address, and several selection bits from the address control function to generate the next microprogram address. The PR-latch jump/test functions use the data held in the PR-latch, the current microprogram address, and several selection bits from the address control function to generate the next microprogram address.

#### **Flag Control Functions**

The flag control functions of the MCU are selected by the 4 input lines designated FC<sub>0</sub>-FC<sub>3</sub>. Function code formats are given in "Flag Control Function summary."

The following is a detailed description of each of the 8 flag control functions.

### Flag Input Control Functions

The flag input control functions select which flag or flags will be set to the current value of the flag input (FI) line.

Data on FI is stored in the F-latch when the clock is low. The content of the F-latch is loaded into the C and/or Z flag on the rising edge of the clock.

#### Flag Output Control Functions

The flag output control functions select the value to which the flag output  $(\overline{FO})$  line will be forced.

#### FLAG CONTROL FUNCTION TABLE

| MNEMONIC | FUNCTION DESCRIPTION                                                                    |

|----------|-----------------------------------------------------------------------------------------|

| SCZ      | Set C-flag and Z-flag to FI. The C-flag and the Z-flag are both set to the value of FI. |

| STZ      | Set Z-flag to FI. The Z-flag is set to the value of FI. The C-flag is unaffected.       |

| STC      | Set C-flag to FI. The C-flag is set to the value of FI. The Z-flag is unaffected.       |

| HCZ      | Hold C-flag and Z-flag. The values in the C-flag and Z-flag are unaffected.             |

#### FLAG OUTPUT CONTROL FUNCTION TABLE

| MNEMONIC | FUNCTION DESCRIPTION                                    |

|----------|---------------------------------------------------------|

| FF0      | Force FO to 0. FO is forced to the value of logical 0.  |

| FFC      | Force FO to C. FO is forced to the value of the C-flag. |

| FFZ      | Force FO to Z. FO is forced to the value of the Z-flag. |

| FF1      | Force FO to 1. FO is forced to the value of logical 1.  |

#### FLAG CONTROL FUNCTION SUMMARY

| TYPE  | MNEMONIC | DESCRIPTION                | FC <sub>1</sub> | 0 |

|-------|----------|----------------------------|-----------------|---|

|       | SCZ      | Set C-flag and Z-flag to f | 0               | 0 |

| Flag  | STZ      | Set Z-flag to f            | 0               | 1 |

| Input | STC      | Set C-flag to f            | 1               | 0 |

| .     | HCZ      | Hold C-flag and Z-flag     | 1               | 1 |

| TYPE   | MNEMONIC | DESCRIPTION        | FC <sub>3</sub> | 2 |

|--------|----------|--------------------|-----------------|---|

|        | FF0      | Force FO to 0      | 0               | 0 |

| Flag   | FFC      | Force FO to C-flag | 1               | 0 |

| Output | FFZ      | Force FO to Z-flag | 0               | 1 |

|        | FF1      | Force FO to 1      | 1 1             | 1 |

| LOAD<br>FUNCTION |                 | NEXT           | ROW   |                |        |                 | NE     | XT COL                | _              |   |

|------------------|-----------------|----------------|-------|----------------|--------|-----------------|--------|-----------------------|----------------|---|

| LD               | MA <sub>8</sub> | 7              | 6     | 5              | 4      | MA <sub>3</sub> | 2      | 1                     | 0              | ] |

| 0                |                 | S              | ee Ad | dress          | Contro | I Functi        | on Sum | mary                  |                | } |

| 1                | 0               | X <sub>3</sub> | $X_2$ | X <sub>1</sub> | $X_0$  | X <sub>7</sub>  | $X_6$  | <b>X</b> <sub>5</sub> | X <sub>4</sub> |   |

NOTE

f = Contents of the F-latch

xn = Data on PX- or SX-bus line n (active low)

#### **ADDRESS CONTROL FUNCTION SUMMARY**

|          |                         |                 | FUNCTION |    |                |                | NEXT ROW       |       |                 |                | 1              | VEXT  | COL            |                       |                |                |                |